# 320 Gbps co-planar stripline Mach-Zehnder modulator on a generic indium phosphide integrated photonics platform

Citation for published version (APA):

Hillier, J., Meighan, A., Hu, Q., Yao, W., van Dommele, A. R., Augustin, L. M., Wale, M. J., & Williams, K. A. (2025). 320 Gbps co-planar stripline Mach-Zehnder modulator on a generic indium phosphide integrated photonics platform. Optics Express, 33(7), 15081-15094. https://doi.org/10.1364/OE.536930

DOI:

10.1364/OE.536930

Document status and date:

Published: 07/04/2025

#### Document Version:

Publisher's PDF, also known as Version of Record (includes final page, issue and volume numbers)

#### Please check the document version of this publication:

- A submitted manuscript is the version of the article upon submission and before peer-review. There can be important differences between the submitted version and the official published version of record. People interested in the research are advised to contact the author for the final version of the publication, or visit the DOI to the publisher's website.

- The final author version and the galley proof are versions of the publication after peer review.

- The final published version features the final layout of the paper including the volume, issue and page numbers.

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- · Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal.

If the publication is distributed under the terms of Article 25fa of the Dutch Copyright Act, indicated by the "Taverne" license above, please follow below link for the End User Agreement:

www.tue.nl/taverne

Take down policy

If you believe that this document breaches copyright please contact us at:

openaccess@tue.nl

providing details and we will investigate your claim.

Download date: 15 Jul 2025

## 320 Gbps co-planar stripline Mach-Zehnder modulator on a generic indium phosphide integrated photonics platform

JAMES ARTHUR HILLIER, 1,\* D AREZOU MEIGHAN, 1 QIAN HU, 2 D HAOSHUO CHEN,<sup>2</sup> WEIMING YAO,<sup>1</sup> RAINIER VAN DOMMELE,<sup>1</sup> LUC AUGUSTIN, 1,3 MICHAEL WALE, 1,4 AND KEVIN WILLIAMS

**Abstract:** We present the design and characterization of co-planar stripline Mach-Zehnder modulators on an InP platform. The co-planar design exhibited 50  $\Omega$  impedance with velocitymatched optical and electrical signals. We investigated devices with a range of design parameters to identify optimal configurations for high bandwidths (≈80 GHz) and state-of-the-art data transmission rates (320 Gbit/s). An equivalent circuit model that enables fast and holistic design space exploration is developed and experimentally verified. The model predicts ~120 GHz bandwidth for optimized modulator dimensions.

Published by Optica Publishing Group under the terms of the Creative Commons Attribution 4.0 License. Further distribution of this work must maintain attribution to the author(s) and the published article's title, journal citation, and DOI.

## Introduction

The growth in data traffic and the demand for higher data rates in optical communication systems have driven significant research efforts to develop high-performance, high-bandwidth electro-optic (EO) modulators that are considered essential components in a wide range of applications, including data center interconnects and telecommunications. The development of modulators with high bandwidths and low driving voltages is critical for enabling energy-efficient, high-speed optical interconnects and increasing the overall capacity of optical communication networks [1]. Furthermore, they are fundamental to any coherent optical communication system [2]. High-speed EO modulators have been widely deployed in optical communications using an array of material platforms for photonic integrated circuits (PICs) [3–5]. InP-based PICs [6–10] offer unique advantages owing to their potential for a wide range of use cases due to their scalable capacity for monolithic integration of lasers, modulators, amplifiers, and photodetectors [11–13]. Moreover, the InP material system is advantageous due to its strong EO effect when utilizing multi-quantum wells to exploit the quantum-confined Stark effect [14], enabling the development of modulators with low half-wave voltages, low loss, and high bandwidth [15,16]. However, there remains a need for further improvement in the bandwidth and efficiency of InP-based MZMs to meet the requirements of next-generation multi-TB/s optical communication systems.

One avenue to improve performance is to explore epitaxial improvements. This approach was taken by Ozaki et al., who employed coherent driver MZMs using capacitively loaded (CL) travelling wave electrodes (TWEs) by co-integrating the modulator with a printed circuit RF interface [17]. They reported a presently state-of-the-art EO bandwidth of over 90 GHz

<sup>&</sup>lt;sup>1</sup>Eindhoven Hendrik Casimir Institute, Eindhoven University of Technology, 5600 MB Eindhoven, The Netherlands

<sup>&</sup>lt;sup>2</sup>Nokia Bell Labs, 600 Mountain Ave., Murray Hill, NJ 07974, USA

<sup>&</sup>lt;sup>3</sup>SMART Photonics, Eindhoven, The Netherlands

$<sup>^4</sup>$ Department of Electronic and Electrical Engineering, University College London, Torrington Place, London WC1E 7JE, UK

<sup>\*</sup>j.a.hillier@tue.nl

combined with an on-chip insertion loss of 6.1 dB and a half-wave voltage of 0.4 V, sufficient for 1 Tb/s/ $\lambda$ -class operation. The high-speed performance arises primarily from the lower optical and RF losses achieved by employing an n-i-p-n heterostructure in the waveguide. Alternatively, there are design-level improvements that may improve device performance on existing foundry platforms such as replacing traditional co-planar waveguide (CPW)-MZMs with co-planar stripline (CPS)-MZMs, which have gained attention for their potential to achieve high bandwidths [18–20]. The CPS design has also demonstrated comparable performance [21] to current state-of-the-art MZMs on the InP platform with alternative novel design approaches [17,22,23]. In general, a CPS transmission line takes less space as compared to a CPW line and enables a relatively larger range of obtainable characteristic impedances. However, a lack of shielding in CPS lines may cause stray coupling to other lines, which could be negated by including ground planes on both sides of the CPS [24]. Unlike conventional CPS transmission lines, where fields extend into free space and contribute to increased leakage loss, the CPS-MZM implementation benefits from field confinement within the depletion region of the waveguide, minimizing stray microwave leakage. For the case of the JePPIX generic foundry platform, the CPS design allows for improved impedance and velocity matching to increase bandwidth and reduce signal attenuation when compared to CPW-MZMs on the same platform, which exhibited a low characteristic impedance ( $\approx 30 \Omega$ ) and microwave index significantly higher than the group index of the waveguide ( $\approx 5 \text{ vs } 3.7$ ) [25]. Design-level modifications via changing geometric parameters could manipulate the characteristic impedance or microwave index, but at the expense of larger microwave losses.

In this study, we explored the potential for further design-level improvements to the CPS-MZM on the JePPIX platform. We investigated the key geometric design parameters that define the device performance and report the full design, fabrication, and characterization process for high-frequency CPS-type EO-MZMs on the InP platform. We built upon previous efforts to develop a semi-analytical and semi-empirical equivalent circuit model [26,27] that allows for optimization of the device performance metrics from raw design parameters such as layer thicknesses, intentional doping, and device geometry. Subsequently, the model validity is demonstrated through comparisons to measured results of a set of fabricated devices with a wide range of geometric design parameters. These results then allow us to identify device designs that achieve co-operatively optimized bandwidth, driving voltage, and length to provide data transmission rates of 320 Gbit/s and unbiased electrical-electrical (EE) bandwidths of 80 GHz. Finally, we apply the developed equivalent circuit model to predict 120 GHz EO bandwidths for further optimized device designs.

#### 2. Methods

#### 2.1. Equivalent circuit model

Well-established methods for the optimization of circuit design (the semi-analytical method of lines [28] and finite difference methods [29]) are computationally intensive, limiting opportunities for a wider range of holistic design space exploration. Alternative methods with lower computational overhead, such as equivalent circuit models, generally rely on empirical and parameter fitting methods to fit the lumped components of the common transmission line theory to the measurement results [30–32]. While such methods provide a means for local optimization [26], the range of validity is limited to the measurement used for fitting. They also limit the ability to gain a deeper understanding of the underlying physical phenomena that govern the broadband operation of the modulator. Gaining such understanding may be key to discovering new pathways for further design optimization not revealed by brute force parameter sweeping techniques. To ensure that all input parameters can be traced back to physical dimensions and measurable material properties, we utilize a computationally efficient, non-iterative, and spatially resolved equivalent circuit model for travelling-wave electrode MZMs. The electronic propagation across the electrode is

resolved purely from the bulk material and conformally mapped [33] dimensional parameters of the modulator building block and both the electrical and EO phenomena are incorporated into the analytical procedure.

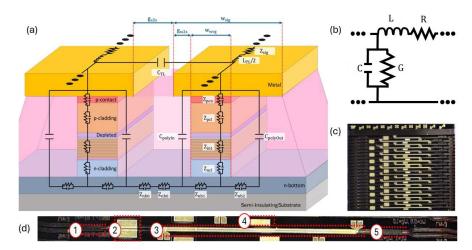

To ensure adherence to physical reality, we expand upon previous iterations of the equivalent circuit methodology [25] to consider a plethora of physical effects that influence device behavior. Specifically, we consider the effect of the doping and material on the carrier mobility and layer conductivity [34–36], the effect of the device design on the microwave velocity [37], the effect of a bias voltage on the depletion width [38] and overlap integral [39], the change in the intrinsic layer conductivity with temperature [37], and the effect of non-planar electrodes. Figure 1(a) presents a schematic illustration of the cross-section of the CPS-MZM design. Further details on the model implementation and formulation of the considered physical effects are provided in Supplement 1. The equivalent circuit presented in Fig. 1(a) can be simplified, considering Kirchhoff's laws. The simplified circuit diagram for a segment of the phase shifter arm is presented in Fig. 1(b). The circuit diagram then matches the fundamental transmission line (TL) [40], such that [41]:

$$L = L'_{eff} \Delta z = Re(R' + L'), \tag{1}$$

$$R = R'_{eff} \Delta z = Im(R' + L')/\omega, \qquad (2)$$

$$G = G'_{eff} \Delta z = Re(Y'), \tag{3}$$

$$C = C'_{eff} \Delta z = Im(Y')/\omega, \tag{4}$$

where  $L'_{eff}$ ,  $R'_{eff}$ ,  $G'_{eff}$ , and  $C'_{eff}$  are the per unit length 'effective' inductance, resistance, conductance, and capacitance, respectively. Z'=1/Y' and Y' are the per unit length impedance and admittance, respectively, of the cross-sectional CPS slice, and  $\omega=2\pi\nu$  is the angular frequency of the RF signal. The prime marker after each symbol indicates the value is per unit length and must be multiplied by the length of the slice,  $\Delta z$ , to give the lumped component values. Effective values are required because the metal impedance and waveguide resistance are complex, with inductive and capacitive components given by the imaginary parts of  $Z'=Z'_{sig}+i\omega L'_{TL}$  and Y' inversely scaled by  $\omega$ . Y' is calculated following a series of steps incorporating Kirchhoff's laws (Supplement 1). The calculation of the equivalent values for the components of simple transmission line theory (Fig. 1(c)) allows for the calculation of the characteristic impedance of the phase modulator,  $Z_0$ , the complex microwave propagation constant,  $\gamma_{\mu}=\alpha_{\mu}+i\beta_{\mu}$  (where  $\alpha_{\mu}$  and  $\beta_{\mu}$  are the attenuation and phase constants) via [42]:

$$Z_0 = \sqrt{\frac{Z'}{Y'}} = \sqrt{\frac{R'_{\text{eff}} + i\omega L'_{\text{eff}}}{G'_{\text{eff}} + i\omega C'_{\text{eff}}}},$$

(5)

$$\gamma_{\mu} = \alpha_{\mu} + j\beta_{\mu} = \sqrt{Z'Y'} = \sqrt{(R'_{eff} + i\omega L'_{eff})(G'_{eff} + i\omega C'_{eff})}, \tag{6}$$

and the microwave group index,  $n_{\mu}$ , is given by  $n_{\mu} = (c_0/\omega)\beta_{\mu}$ , where  $c_0$  is the free space speed of light. To derive the relevant model input values (per unit length conductance,  $G_L^{'}$ , capacitance,  $C_L^{'}$ , and complex impedance,  $\widetilde{Z'}_L$ ) from the intrinsic properties of each layer, we consider the underlying physical phenomena that cause individual epitaxial layers to act as combinations of lumped-element resistors and capacitors [43,44]. Considerations are also made for the per unit length inductance of the transmission line,  $L'_L$  [45]. The values for each lumped component in Fig. 1(a) are derived from the input physical parameters [26], tailoring a suite of relationships previously collated for the case of a CPW-MZM [25]. The input parameters of the equivalent circuit model, listed in Table 1, are based on specifications for the fabricated chips.

**Fig. 1.** (a) Cross-sectional schematic of the co-planar strip (CPS) Mach-Zehnder modulator (MZM), showing the (not to scale) optical waveguide and electrode arrangement. Superimposed onto the schematic is the equivalent circuit model used for simulation and performance analysis. (b) Schematic circuit diagram for a simple transmission line (TL), equivalent to (a) through Kirchoff's laws. (c) Top-down microscope image of the chip, showing the array of CPS-MZM devices alongside waveguide and radio frequency (RF) pad test structures. (d) Zoomed-in image of the chip showing a single CPS-MZM device comprising input and output multi-mode interferometers (MMIs; (1) and (5), respectively), pre-device DC phase shifters (2), 1 mm long phase-shifter electrodes (3), and a DC pad (4).

Table 1. Input parameters of the equivalent circuit model including the thickness,  $d_L$ , static permittivity ratio,  $\epsilon_{sr,L}$ , and intentional doping,  $N_L$ , of each epitaxial layer.

| Layer<br>Metal | Thickness, d <sub>L</sub> (μm) | Static Permittivity Ratio, $\epsilon_{sr,L}$ | Intentional Doping, $N_L$ (cm <sup>-3</sup> ) $n/a$ |

|----------------|--------------------------------|----------------------------------------------|-----------------------------------------------------|

|                |                                |                                              |                                                     |

| p-cladding     | 1.3                            | 12.35                                        | $3.0 \times 10^{17}$                                |

| n-buffer       | 0.20                           | 12.35                                        | $2.0 \times 10^{16}$                                |

| Intrinsic      | 0.58                           | 13.32                                        | $n.i.d(\sim 1 \times 10^{14})$                      |

| n-cladding     | 7.5                            | 12.35                                        | $5.0 \times 10^{17}$                                |

| n-bottom       | 1.5                            | 12.35                                        | $1.0\times10^{18}$                                  |

| Polyimide      | 2.3                            | 2.260                                        | n/a                                                 |

#### 2.2. Electric bandwidth simulation

The Keysight Advanced Design System (ADS) environment was used to perform simulations of the S-parameters for a two-port configuration with source impedance,  $Z_S$ , and load impedance,  $Z_L$ . To represent the ground-signal probes used for EE measurements, only two ports are used and connected to a single arm of the CPS-MZM model, which contains 30 discrete cross-sectional slices that comprise the entire electrode length,  $l_{ps}$ . The second arm is connected to the shared ground. A DC voltage source is connected to the n-bottom layer. The simulation outputs the two-port RF frequency-dependent scattering matrix S(v), comprising the S-parameters $S_{21}(v)$ ,  $S_{11}(v)$ ,  $S_{12}(v)$ , and  $S_{22}(v)$  alongside the group delay matrix,  $\Delta t_g(v)$ , for the device (i.e., CPS-MZM including RF pads). From these results, one separates the equivalent circuit for just the transmission line (excludes RF pads) to derive the device's characteristic impedance,  $Z_{C,dev}(v)$ , propagation constant,  $\gamma_{dev}$ , and microwave index,  $n_{\mu,dev}(v)$ . The -6 dB electrical-electrical (EE)

bandwidth for each propagation direction is extracted from  $S_{21}(\nu)$ . We utilize a frequency range of 1-200 GHzwith steps of 1 GHz. Variable parameters are swept using 50 discrete values across a range of interest for each parameter. The implementation of the equivalent circuit model from material properties [46] to the device performance metrics is detailed further within Supplement 1.

#### 2.3. Fabricated devices

To validate the outlined equivalent circuit model, an array of 22 devices was fabricated on a single  $4.6 \text{ mm} \times 4.0 \text{ mm}$  chip. An indicative set of geometric design variables (waveguide width,  $w_{\text{wvg}}$ , signal track width, w<sub>sig</sub>, and signal-signal gap, w<sub>s2s</sub>; see Table 2) were adjusted across each 'lane'. Each lane comprised electrode lengths along the propagation direction of 1 mm and 2 mm. The varied device geometry variables were chosen to cover a range of simulated results while ensuring device functionality at the foundries' lower design rule limits. The CPS-MZMs were created using the JePPIX process design kit [47,48] and fabricated on the InP generic platform at SMART photonics [13] using a semi-insulating substrate and a process adaptation for the multi-quantum well (MOW) modulator layer stack where the active layer bandgap was  $1.39 \pm 0.02 \, \mu m$ . Vitally, this platform enables co-integration of the CPS-MZMs with lasers, SOAs, and other on-chip devices, provided an additional MQW regrowth step to enable high-performance lasers and modulators on the same chip [12]. Figure 1(c) presents a microscope image of the fabricated chip, comprising an array of phase shifter electrodes, input/output 2 × 2 multi-mode interferometers (MMIs), and DC phase shifters.  $2 \times 2$  multi-mode interferometers (MMIs) allowed for optical input and output redundancy. The MZM length defined from the input of the first MMI to the last is 1.7 mm and 3.7 mm for the 1 mm and 2 mm electrode lengths, respectively.

Signal width,  $w_{sig} \; (\mu m)$ Waveguide width,  $w_{wvg}$  ( $\mu m$ ) Signal-signal gap, w<sub>s2s</sub> (µm) 0.7 7.0 0.8 10 7.0 7.0 1.0 10 0.9 10 7.0 1.2 10 7.0 1.5 10 7.0 1.0 5.0 7.0 1.0 15 7.0 20 7.0 1.0 1.0 10 5.0 1.0 10 15 1.0 10 20

Table 2. Varied geometric parameters for the fabricated devices

#### 3. Results

#### 3.1. Optical and travelling wave electrode electronic performance

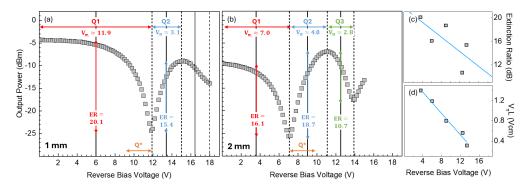

Determination of  $V_\pi L$  was performed by sweeping reverse bias voltage,  $V_{rb}$ , from 0-15 V in steps of 0.2 V. A polarization controller ensured transverse-electric mode input by maximizing the modulation depth. The insertion losses for the full 1 mm device were estimated to be  $9.1 \pm 0.8$  dB, excluding the optical coupling losses of 2.5 dB/facet between the modulator chip and the lensed fiber (5  $\mu$ m mode field diameter). Figure 2 presents static optical power measurements for the 'optimized' devices, where  $w_{wvg} = 0.8$ ,  $w_{sig} = 10$ , and  $w_{s2s} = 7$ , for the

CPS-MZM devices with electrode lengths of (a) 1 mm and (b) 2 mm. The curves are cosine-line but with a decreasing period and amplitude with increasing bias voltage. This is due to the quadratic terms for the electro-optic efficiency and a growing depletion zone that increases the overlap of electric and optical fields (see Supplement 1). The result is the existence of multiple quadrature points within the swept voltage range where  $V_{\pi}$  and the static extinction ratios (ER) are different for each quadrature point. The '1st quadrature-point' (red arrows and labels) was found to be at 6 V and 7 V for the devices and electrode lengths of 1 mm and 2 mm, respectively, by . The corresponding values of  $V_{\pi}$  were 11.9 V and 7 V ( $V_{\pi}L=1.3\pm0.1$  Vcm) and the corresponding static extinction ratios (ERs) were 20.1 dB and 15.4 dB, respectively.

**Fig. 2.** Indicative  $V_\pi$  curves for the best-performing co-planar strip Mach-Zehnder modulator devices. Output power in dBm vs reverse bias voltage (V) for devices with electrode lengths of 1 mm and 2 mm, respectively, and a waveguide width of 0.8 μm, signal width of 10μm, and signal-signal gap of 7 μm. The individual operation regions around each quadrature point (Q1, Q2, Q3) are labelled along with their half-wave-voltage,  $V_\pi$ , and extinction ratio. (c) and (d) show the measured extinction ratio and  $V_\pi$ -length product, respectively. The solid blue lines in (c) and (d) serve to quickly estimate the performance metrics for a given reverse bias voltage.

Under operation, however, a higher  $V_{rb}$  would be used to ensure a larger depletion region exist within the waveguide core layer. For the 1 mm device a  $2^{nd}$  quadrature point exists at 13.4 V with a significantly lower  $V_{\pi}$  of 3.1 V at the expense of a lower static ER of 17.0 dB. For the 2 mm device there are two additional quadrature points within the swept voltage range. The  $2^{nd}$  quadrature point again has a significantly lower  $V_{\pi}$  of 4.0 V but with a larger ER of 18.7 dB. The larger ER likely arises from a phase difference between the two arms at 0V such that optical power at 0V is not at the maximum. The  $3^{rd}$  quadrature point has an even lower  $V_{\pi}$  of 2.8 V but the expense of a sharp reduction in the ER to 10.7 dB. The dependence of  $V_{\pi}L$  and ER on the reverse bias voltage makes reporting general performance metrics for the device non-trivial. Instead, we plot ER and  $V_{\pi}L$  against the reverse bias voltage in Fig. 2(c) and Fig. 2(d), respectively. We show a linear fit to aid in the estimation of the performance metrics given  $V_{bi}$ .

To verify the predicted beyond-100 GHz performance of the CPS modulator design [19], we conducted small-signal measurements of  $S_{21,EE}$  using a Keysight PNA-X Series vector network analyser (VNA). A swept RF signal with a power of -5.0 dBm was applied over a frequency range of 1.7-110 GHz in steps of 0.034 GHz. The RF signal power from the  $50~\Omega$  VNA system was inputted into and received from the modulator electrode using 1 mm diameter, 20 cm long coaxial cables connected to ground-signal (GS) RF probes with -6 dB EE bandwidths of  $\approx 110$  GHz. The RF probes were de-embedded using short-open-load-through measurements using a calibration substrate. Due to an inability to reliably attach additional DC probes to the utilized automated probe system, all measurements were performed without applying DC bias

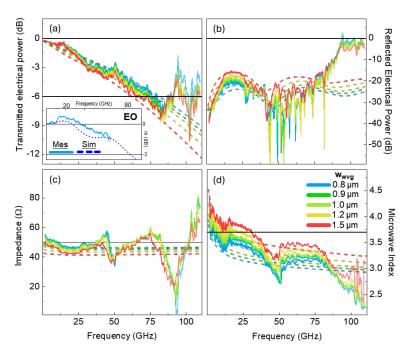

to the n-bottom layer. Figure 3 presents (a) the port-1 to port-2 transmitted electrical power,  $S_{21}(\nu)$ , (b) the port-1 to port-1 reflected electrical power,  $S_{11}(\nu)$ , the input impedance,  $Z_{in}(\nu)$ , and (d) the microwave phase index,  $n_{\mu}(\nu)$ , for the set of measurable devices on Sample 1 for the devices exhibiting variations of  $w_{wvg}$  from  $0.8-1.5~\mu m$  (solid blue-red lines) where  $w_{sig}=10$  and  $w_{s2~s}=7$ . In all plots, the dashed lines represent the simulated data using the geometries of the measured devices. In the inset of (a) we present the measured (solid cyan line) and simulated (dashed blue line) electro-optic frequency response a single device (the best performing device  $(w_{wvg}=0.8~\mu m,\,w_{sig}=10,\,and\,w_{s2~s}=7)$ . See Supplement 1 for the full set of measurements for variations in electrode width and electrode gap for both device lengths. As the cross-sectional equivalent circuit model can be reduced to a simple TL, the signal propagation is completely defined by  $Z_0$  (Eq. (5)) and  $\gamma_{\mu}$  (Eq. (6)) along with boundary conditions at the input and output [49]:

$$V(v) = \frac{1}{l_{ps}} \int_{l_{ps}} v(z, v) dz = \frac{V_g(1 + \rho_1)}{2} \cdot \frac{e_0^{j\beta l_{ps}}(V_+ + \rho_2 V_-)}{e_e^{j\beta l_{ps}} - \rho_1 \rho_2 e_e^{-j\beta l_{ps}}},$$

(7)

where  $V_g$  is the source voltage while  $V_+$  and  $V_-$  are the forward and backward travelling voltage signal amplitudes, respectively.  $P_1 = (Z_0 - Z_S)/(Z_0 + Z_S)$  and  $\rho_2 = (Z_L - Z_0)/(Z_L + Z_0)$  are the RF source and load reflections, respectively. This allows for extraction of predicted  $S_{21}(v)$ ,  $S_{11}(v)$ ,  $Z_{in}(v)$ , and  $n_u(v)$  values from the equivalent circuit model, where the influence of the RF pads is accounted for by considering the pads as lumped TL elements where the TL parameters were fit to measurements of the RF test pad structures (see Fig. 1(b)). The predicted trends are evident across all functional devices up to ≈80 GHz. However, we note that there are notable irregularities in each of the presented plots both above and below this frequency (e.g. the sharp jumps in  $S_{21}(v>80 \text{ GHz})$ ). We note the observed spiking at 12.5 GHz and 40 GHz that can attributed to stray parasitic effects, specifically arising from the RF pads, transition regions, and associated impedance mismatches. Such parasitic effects are not presently included in the simulation model. Major irregularities above 80 GHz arise from the measurement calibration and are expected to affect only the data above ≈80 GHz (see Supplement 1 for an investigation into the calibration). We thus limit any extraction of parameters in further analysis to frequencies up to 80 GHz. We highlight this region in the plots by showing this part of the measurement data width reduced line thickness.

The extracted EE bandwidth,  $BW_{EE}$ , of  $80\pm 8$  GHz for a 1 mm long MZM where  $w_{wvg}=0.8$ ,  $w_{sig}=10$ , and  $w_{s2\;s}=7$  is comparable to state-of-art for InP [17,22,23]. This represents a significant improvement over previously reported values for CPW-MZMs fabricated using the JePPIX generic foundry process [50]. It should also be noted that the S-parameters and the extracted parameters such as the -6 dB EE bandwidth are for the device operating under no reverse bias voltage. Due to the increasing depletion zone depth, the bandwidth increases significantly with high reverse bias voltages. The equivalent circuit model outlined in this work predicts that the EE bandwidth raises from 80 GHz to 93 GHz for a reverse bias voltage of 10.6 V (see Supplement 1). The inset in Fig. 2(a) presents the EO frequency response of the best-performing device ( $w_{wvg}=0.8~\mu m$ ,  $w_{sig}=10~\mu m$ , and  $w_{s2\;s}=7~\mu m$ ) to demonstrate that due to the close velocity and impedance matching of the CPS-MZM devices, the observed EE transmission effectively translates into a similar EO bandwidth of  $\approx 90~\text{GHz}$ .

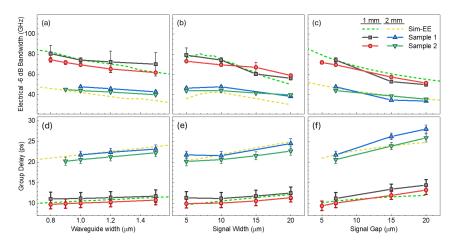

A vital aspect of the equivalent circuit model verification is to elucidate the precise trends and mechanisms for how the device performance indicators (bandwidth, group delay) are influenced by the geometric parameters used to optimize the device. Therefore, Fig. 4 presents comparisons of measured (symbols) and simulated (dotted line) (a-c)  $BW_{EE}$ , and (d-f)  $\Delta t_g$  for variations in the  $w_{wg}$ ,  $w_s$ , and  $w_{s2\,s}$ , respectively, and for both devices with electrode lengths of 1 mm (red circle symbols, grey square symbols, dashed green line) and 2 mm (blue triangle symbols, green triangle symbols, dashed yellow line). The two sets of measured devices for each electrode length

**Fig. 3.** (a) Port-1 to port-2 transmitted electrical power,  $S_{21,EE}(\nu)$  (dB), (b) port-1 to port-1 EE reflection,  $S_{11,EE}(\nu)$  (dB), (c) input impedance,  $Z_{in}(\nu)$ , and (d) microwave phase index,  $n_{\mu}(\nu)$ , and for the set of functional devices (Sample 2, 1 mm electrode lengths) with variations in the waveguide width,  $w_{wvg}$ : 0.8 μm (blue), 0.9 μm (green), 1.0 μm (light green), 1.2 μm (yellow), and 1.5 μm (red), where  $w_{sig}=10$  and  $w_{s2\,s}=7$ . In all plots, the dashed lines with a corresponding colour scheme indicate the simulated results for each fabricated device. The change in measured line intensity after 85 GHz indicates the range where measurements show abnormalities are excluded from further analysis. In (a), the horizontal line at 6 dB helps to indicate the -6 dB EE bandwidth. In (c), the horizontal line at 50 Ω indicates the source/load impedance. In (d), the horizontal line at 3.7 indicates the effective optical index. The inset of (a) presents the measured (solid cyan line) and simulated (dashed blue line) electro-optic frequency response for device with  $w_{wvg}=0.8$  μm  $w_{sig}=10$  and  $w_{s2\,s}=7$ , adapted from [25].

show results for two independently measured chips, providing insights into device performance variation due to fabrication tolerances. In general, measurement and simulated results demonstrate an increase in  $BW_{EE}$  alongside a decrease in  $\Delta t_g$  as each geometric parameter decreases. A reasonable agreement was observed between simulations and measurements across the range of geometric design variables, device lengths, and samples. This validates the equivalent circuit model's predictive capacity within and beyond the currently measurable parameter space. Inspecting the formulation of the model while sweeping the input parameters and observing the effect on not only the device performance metrics but the incremental lumped component properties enable one to glean insights into the interplay of the geometric parameters on the device performance to better understand the optimization of the performance metrics. For example, we note from Fig. 4(a) how reducing waveguide width increases  $BW_{EE}$ . This can be understood as the reduction of the area of the effective capacitor plates on either side of the depletion zone where the optical mode resides ( $C'=\epsilon_8 A_\perp/l_\parallel$ ) [37].

A smaller capacitance decreases the RC time constant, increasing  $BW_{EE}$ . Minor bandwidth gains also arise from the reduction of the conductance of the p-contact, p-cladding, and n-cladding

**Fig. 4.** Comparisons of measured devices (grey and red symbols) and simulated (dashed green line) (a)–(c) –6 dB electrical-electrical (EE) bandwidth, BW<sub>EE</sub> (GHz), and (d)–(f) group delay,  $\Delta t_g$  (ps), for variations in the (a), (c) waveguide width,  $w_{wvg}(\mu m)$ , (b), (e) signal track width,  $w_{sig}(\mu m)$ , and the (c), (f) signal gap width,  $w_{s2 s}(\mu m)$ .

layers  $(G'_y = \sigma_y d_y/w_w)$  [37]. However, the reduction of  $w_{wvg}$  also increases the capacitance between the signal electrodes and n-bottom layer ( $C_{polyOut}^{'} = \epsilon_0 \epsilon_r (w_{sig} - w_{s2~g} - w_{wvg})/d_{wvg}$ ). In the end, the increased electrode capacitance negates some, but not all, of the expected EE bandwidth gains. We can also build a picture of the competition of various parameters with dependencies on the w<sub>sig</sub> affect the final device's performance. Figure 4(b) shows that reducing  $w_{sig}$  increases  $BW_{EE}$  up to an optimal value of ~80GHz at 7  $\mu m$  where further reductions in  $w_{sig}$  reduce  $BW_{EE}$ . One may expect that the TL inductance,  $L'_{TL}$ , is a primary driver of the dip in performance for low  $w_{sig}$ . Indeed, reducing  $w_{sig}$  increases  $L'_{TL}$  and this leads to a significant reduction in BW<sub>EE</sub>. The effect of w<sub>sig</sub> on the inductance is more prominent for lower signal widths, which also contributes to the decline in  $BW_{EE}$  when  $w_{wig} {<} 7~\mu m$ . However, clearly identifying the precise mechanisms that govern properties we are interested in such as the precise position and height of the peak in BW<sub>EE</sub>(w<sub>sig</sub>) is not so trivial. This is because there exist a multitude of dependencies of wsig on the parameters that define the lumped components, alongside  $L'_{TL}$ , such as the electrode impedance,  $Z' = \eta_{mtl}/w_{sig}$ , the capacitance between the electrodes and n-bottom layer, and the capacitance through air, Cair. Firstly, the electrode impedance increases with reduced  $w_{sig}$ . This increases RF losses in a way that the (normalized) bandwidth is increased. However, this comes at the cost of reducing signal intensity at low RF frequency. Reducing  $w_{sig}$  also increases the characteristic impedance,  $Z_0$ , which can increase or decrease BW<sub>EE</sub> depending on whether the  $Z_0$  shift brings  $Z_0$  closer or further from 50  $\Omega$ . In the case where all other variables remain at their default value, the characteristic impedance is 50  $\Omega$  at ~7  $\mu$ m. Therefore, we note how  $Z_0$  is a key driver of the position of the peak in  $BW_{EE}$  that currently resides at  ${\sim}7~\mu m$  for the default geometry used in this work. Alterations in other geometric parameters may allow for tuning of this peak to take further advantage of the bandwidth gains from a thinner electrode, potentially enabling further optimization of the device performance.

#### 3.2. Experimental large signal electro-optic performance

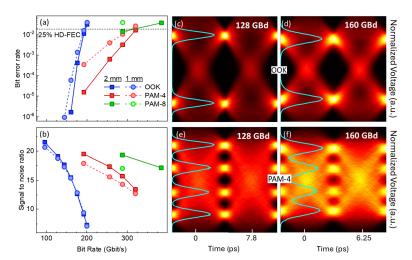

To highlight the performance gains of the CPS-MZMs on the JePPIX platform, we utilized the above outlined devices to modulate large signals using state-of-the-art post-processing methods to extract as much performance as possible. OOK, PAM-4, and PAM-8 signals were generated

across a symbol rate of 96 - 200 GBd using a peak-to-peak driving voltage,  $V_{pp}$ , of 2.7 V. To account for a  $V_{pp}$  lower than  $V_{\pi}$ ,  $V_{rb}$  was adjusted to maximize the ER. The resulting relatively large  $V_{rb}$  of  $\approx 13$  V (shown with Q\* in Fig. 2) is however undesirable as this can limit further integration with electronics. Methods to further reduce  $V_{\boldsymbol{\pi}}$  at lower bias voltages, such as optimization of the multi-quantum wells and/or alternative layer stacks [17], are highly warranted. Further measurement and signal processing details are provided in Supplement 1 [51]. Figure 5 presents the outcomes of these large-signal measurements post-equalization when utilizing OOK (blue), PAM-4 (red), and PAM-4 (green) modulation formats. Figures 5(a) and 5(b) show the bit error rate (BER) and SNR, respectively, for the measured symbol rates, as measured on the best-performing CPS-MZM devices (where  $w_{wvg} = 0.8 \mu m$ ,  $w_{sig} = 10 \mu m$ , and  $w_{s2 s} = 7 \mu m$ ) with electrode lengths of 1 mm (circle symbols; dashed lines) and 2 mm (square symbols; solids lines). The devices with electrode lengths of 1 mm displayed lower SNR across all symbol rates, despite an ostensibly larger -6 dB EE bandwidth. This is attributed to the larger effective extinction ratio for the devices with electrode lengths of 2 mm. With OOK modulation, no bit errors were detected up to 160 GBd. However, bit errors appeared at 160 GBd and the BER increased with higher symbol rates, crossing the 25 % overhead HD-FEC threshold [52] between 192 GBd and 200 GBd. For PAM-4, the BER remained under the HD-FEC threshold up to 160 GBd.

**Fig. 5.** (a) Bit error rates and (b) signal-noise ratios at the measured symbol rates using OOK (blue), PAM-4 (red), and PAM-8 (green) modulation formats for the best-performing modulators with electrode lengths of 2 mm (square symbols, solid lines) and 1 mm (circle symbols, dashed lines). Alongside are the eye diagrams for (c),(d) OOK and (e),(f) PAM-4 modulation formats at 128 GBd and 160 GBd, respectively. Eye histograms are superimposed onto each eye diagram (cyan lines). Eye diagrams are generated after digital signal processing (including filtering, equalization, and DC removal), and so the voltage axis is in arbitrary units.

This corresponds to a line rate of 320 Gbit/s from which we calculate a bit rate of 256 GBit/s (see Supplement 1). Eye diagrams for the device with electrode lengths of 2 mm, illustrated in Fig. 5(c)-(f) for OOK and PAM-4 modulations at 128 and 160 GBd, respectively, reveal open eyes for OOK and increasingly constrained eyes for PAM-4.

## 3.3. Predicted 120 GHz electro-optic bandwidth for optimized designs

To investigate the optimization of the geometric parameters on the device performance, particularly the EO bandwidth, we employed the equivalent circuit model outlined in this work and corroborated it with empirical data from our fabricated devices. An iterative optimization process focused on maximizing the EO bandwidth for a 50  $\Omega$  source and load impedance,  $Z_S = Z_T$  and an optical effective group index of 3.7. We determined the following optimal geometric parameters:  $w_{wvg} = 0.6~\mu m$ ,  $w_{sig} = 3.8~\mu m$ ,  $w_{w2s} = 0.3~\mu m$ ,  $w_{s2~s} = 3.6~\mu m$ , and  $V_{DC} = 10V$ . These dimensions were found to significantly enhance the modulator's EO bandwidth. An electrode length, L, of 1 mm was selected for the simulation to facilitate a direct comparison with the 1 mm fabricated devices that exhibit larger bandwidths. It should be noted that the inherent trade-off between the  $V_{\pi}L$ , product and microwave losses requires a compromise in electrode length; adjusting L could be used to optimize either modulation efficiency or EO bandwidth depending on specific performance requirements. It is also notable that the optimized  $w_{sig}$  is lower than the bandwidth peak observed in Fig. 4(b). This is due to the interplay between the different parameters with the geometry, such that changing the other geometric parameters ( $w_{wvg}$ ,  $w_{s2~s}$ ,

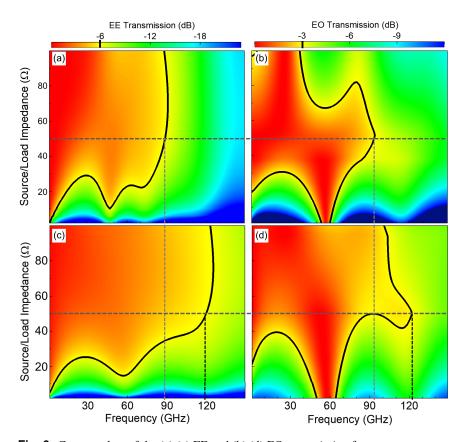

**Fig. 6.** Contour plots of the (a),(c) EE and (b),(d) EO transmission for a sweep across a wide range of source/load impedance,  $Z_S = Z_T$ , and RF frequency,  $\nu$ , for the (a),(b) 'default' fabricated sample ( $w_{wvg} = 1.0~\mu m$ ,  $w_{sig} = 10~\mu m$ ,  $w_{w2~s} = 1.5~\mu m$ ,  $w_{s2~s} = 7~\mu m$ , L = 1 mm) and (c),(d) an 'optimized' sample ( $w_{wvg} = 0.6~\mu m$ ,  $w_{sig} = 3.8~\mu m$ ,  $w_{w2~s} = 0.3~\mu m$ ,  $w_{s2~s} = \mu m$ , L = 1~mm). The solid black line indicates where the EE and EO transmission drops to 6 dB and 3 dB below its static value, respectively (i.e., EE and EO bandwidth). The horizontal grey dashed line indicates  $Z_S = 50~\Omega$ . The vertical dashed lines aid the eye to observe the EE and EO bandwidths.

$w_{w2\;s})$  shifted the bandwidth peak to below 7um. The optimized design features dimensions that are somewhat smaller than those in our current fabricated devices, which were designed near the tolerance limits at the time fabrication. However, in the generic InP process, deep-UV scanner lithography is used for waveguide etch lithography, with a critical dimension of approximately 100 nm making a target  $w_{wvg}$  of 0.6  $\mu m$  currently feasible [53]. Similarly, several published lift-off processes have demonstrated sub-micron resolution for metal structures, indicating that a metal electrode width and gap of <3.8  $\mu m$  is also feasible [54,55]. Although the present process does not routinely yield 3.6  $\mu m$  structures at high yield, lift-off processes can be further adapted to achieve this.

Furthermore, as detailed in the JePPIX Roadmap 2021–2025 [56], ongoing improvements in process uniformity and increased wafer capacity are already enabling tighter tolerances, with many of these advanced capabilities being realized in recent production runs. Figure 6 presents contour plots of the (a,c) EE and (b,d) EO transmission for the simulated device with (a-b) pre- and (c-d) post-optimized geometric parameters. The pre-optimized film represents the 'default' sample where  $w_{wvg} = 1.0 \mu m$ ,  $w_{sig} = 10 \mu m$ ,  $w_{w2 s} = 1.5 \mu m$ ,  $w_{s2 s} = 7 \mu m$ , and L=1 mm. To produce these contours, we performed a sweep across a range  $Z_S$   $(1-100~\Omega)$ and v (1-150 GHz). The resulting contour plots are illustrative of the RC roll-off characteristics and exhibit the dependency of the EE and EO bandwidth on Z<sub>S</sub>, as demarcated by the solid black contours. The EE bandwidth shows clear interference fringes when  $Z_S$  is less than  $\approx 40~\Omega$ , due to back-reflections from the load. As the EO bandwidth was optimized with the constraint of  $Z_S = 50 \Omega$ , it is not surprising that the maximum EO bandwidth occurs when the CPS-MZMs also have an impedance of 50  $\Omega$ . The EO transmission follows the EE transmission closely, but the effect of impedance mismatch is greatly exaggerated, creating an 'island' of enhanced EO bandwidth up to 120 GHz at around 50 Ω. Enhancements to the EO bandwidth do not come purely from the better impedance mismatch, but also from the better velocity matching between the electronic and optical signal [57], the use of a non-zero reverse bias voltage increasing the depletion zone width (see Supplement 1), as well as reductions in the impedance, inductance, capacitance, and acceptance of the electronic TL.

#### 4. Conclusions

An equivalent circuit model was developed to evaluate device performance. The semi-analytical nature of the model demonstrated utility for rapid, holistic, and extensive parameter optimization while the use of controllable input values (device geometry, epitaxial layer doping, epitaxial layer thicknesses) elucidated the mechanisms that govern the performance metrics. Employing design optimizations predicted ~120 GHz EO-bandwidth for future devices adhering to current specifications for foundry InP multi-project wafers. The equivalent circuit model was verified through a series of fabricated devices, showcasing bandwidths in the 60-90 GHz range with bias-dependent  $V_{\pi}L$  and ER ranging between 0.31-1.4 Vcm and 10.7-20.1 dB, respectively. We show capacity for open eye diagrams at 256 Gbit/s and line error rates within the permissible BER thresholds for overhead HD-FEC at a line rate of 320 Gbit/s. Hereby, we verify that the CPS-MZM design provides a significant enhancement of the EO bandwidth and data modulation capacity over the traditional CPW design using the JePPIX-based generic InP platform.

Funding. Nederlandse Organisatie voor Wetenschappelijk Onderzoek.

**Disclosures.** The authors declare no conflicts of interest.

Data availability. Data underlying the results presented in this paper are available in Supplement 1.

Supplemental document. See Supplement 1 for supporting content.

#### References

1. L. Thylén and L. Wosinski, "Integrated photonics in the 21st century," Photonics Res. 2(2), 75 (2014).

- G. L. Li and P. K. L. Yu, "Optical intensity modulators for digital and analog applications," J. Lightwave Technol. 21(9), 2010–2030 (2003).

- M. Kohli, D. Chelladurai, A. Messner, et al., "Plasmonic Ferroelectric Modulator Monolithically Integrated on SiN for 216 GBd Data Transmission," J. Lightwave Technol. 41(12), 3825–3831 (2023).

- M. Zhang, C. Wang, X. Chen, et al., "Ultra-High Bandwidth Integrated Lithium Niobate Modulators with Record-Low Vπ," in Optical Fiber Communications Conference and Exposition (IEEE, 2018), pp. 1–3.

- G. Sinatkas, T. Christopoulos, O. Tsilipakos, et al., "Electro-optic modulation in integrated photonics," J. Appl. Phys. 130(1), 010901 (2021).

- F. A. Kish, D. Welch, R. Nagarajan, et al., "Current Status of Large-Scale InP Photonic Integrated Circuits," IEEE J. Sel. Top. Quantum Electron. 17(6), 1470–1489 (2011).

- G. E. Hoefler, Y. Zhou, M. Anagnosti, et al., "Foundry Development of System-On-Chip InP-Based Photonic Integrated Circuits," IEEE J. Sel. Top. Quantum Electron. 25(5), 1–17 (2019).

- F. Kish, V. Lal, P. Evans, et al., "System-on-Chip Photonic Integrated Circuits," IEEE J. Sel. Top. Quantum Electron. 24(1), 1–20 (2018).

- S. Chandrasekhar, L. Xiang, P. J. Winzer, et al., "Compact All-InP Laser-Vector-Modulator for Generation and Transmission of 100-Gb/s PDM-QPSK and 200-Gb/s PDM-16-QAM," J. Lightwave Technol. 32(4), 736–742 (2014).

- R. A. Griffin, S. K. Jones, N. Whitbread, et al., "InP Mach–Zehnder Modulator Platform for 10/40/100/200-Gb/s Operation," IEEE J. Sel. Top. Quantum Electron. 19(6), 158–166 (2013).

- 11. M. Smit, K. Williams, and J. van der Tol, "Past, present, and future of InP-based photonic integration," APL Photonics 4(5), 050901 (2019).

- L. M. Augustin, R. Santos, E. Den Haan, et al., "InP-Based Generic Foundry Platform for Photonic Integrated Circuits," IEEE J. Sel. Top. Quantum Electron. 24(1), 1–10 (2018).

- 13. R. A. Griffin, N. D. Whitbread, S. K. Jones, et al., "InP Coherent Optical Modulator with Integrated Amplification for High Capacity Transmission," in *Optical Fiber Communication Conference* (OSA, 2015), paper Th4E.2.

- 14. J. E. Zucker, I. Bar-Joseph, B. I. Miller, *et al.*, "Quaternary quantum wells for electro-optic intensity and phase modulation at 1.3 and 1.55 µm," Appl. Phys. Lett. **54**(1), 10–12 (1989).

- Y. Ogiso, Y. Hashizume, H. Tanobe, et al., "80-GHz Bandwidth and 1.5-V V<sub>π</sub> InP-Based IQ Modulator," J. Lightwave Technol. 38(2), 249–255 (2020).

- Y. Ogiso, J. Ozaki, Y. Ueda, et al., "Ultra-High Bandwidth InP IQ Modulator for Beyond 100-GBd Transmission," Ultra-High Bandwidth InP IQ Modulator for Beyond 100-GBd Transmission," in Optical Fiber Communications Conference and Exhibition (IEEE, 2019).

- 17. J. Ozaki, Y. Ogiso, Y. Hashizume, *et al.*, "Over-85-GHz-Bandwidth InP-Based Coherent Driver Modulator Capable of 1-Tb/s/λ-Class Operation," J. Lightwave Technol. **41**(11), 3290–3296 (2023).

- A. Meighan, M. J. Wale, and K. A. Williams, "High-Density Coplanar Strip-Line Mach-Zehnder Modulators in a InP Generic Platform," in European Conference on Optical Communication (IEEE, 2021), pp. 1–3.

- 19. A. Meighan, L. Augustin, M. J. Wale, et al., "High-Density 100 GHz-Class Mach-Zehnder Modulators integrated in a InP Generic Foundry Platform," in Conference on Lasers and Electro-Optics (IEEE, 2022), pp. 1–3.

- 20. A. Meighan, W. Yao, M. J. Wale, et al., "Design of 100 GHz-class Mach-Zehnder modulators in a generic indium phosphide platform," in *Photonics Conference* (IEEE, 2020), pp. 1–2.

- 21. J. A. Hillier, A. Meighan, M. Van Den, *et al.*, "A 100 GBaud co-planar stripline Mach-Zehnder modulator on Indium Phosphide platform," in *Opto-Electronics and Communications Conference* (IEEE, 2023), pp. 1–3.

- 22. Y. D. Gupta, G. Binet, W. Diels, et al., "Highest Performance Open Access Modulators on InP Platform," in European Conference on Optical Communication (IEEE, 2022), pp. 1–3.

- 23. J. Xing, C. Sun, B. Xiong, et al., "Over 40 GHz Bandwidth and 0.7-V Vπ Compact InP-Based Electro-optic Modulator with n-i-n MQBs," in Asia Communications and Photonics Conference (IEEE, 2022), pp. 1431–1433.

- A. K. Verma, Introduction to Modern Planar Transmission Lines: Physical, Analytical, and Circuit Models Approach, 1st ed. (Wiley, 2021).

- A. Meighan, Co-design of the High-speed Photonic and Electronic Integrated Circuits (Eindhoven University of Technology, 2021).

- 26. W. Yao, G. Gilardi, M. K. Smit, et al., "Equivalent circuit modelling of integrated traveling-wave optical modulator in InP foundry platform," in 18th European Conference on Integrated Optics (2016), pp. 1–2.

- 27. H. Yu and W. Bogaerts, "An Equivalent Circuit Model of the Traveling Wave Electrode for Carrier-Depletion-Based Silicon Optical Modulators," J. Lightwave Technol. **30**(11), 1602–1609 (2012).

- 28. U. Rogge and R. Pregla, "Method of lines for the analysis of strip-loaded optical waveguides," J. Opt. Soc. Am. B **8**(2), 459 (1991).

- J. Witzens, T. Baehr-Jones, and M. Hochberg, "Design of transmission line driven slot waveguide Mach-Zehnder interferometers and application to analog optical links," Opt. Express 18(16), 16902 (2010).

- 30. B. Roycroft, P. Morrissey, Wei Han, et al., "Efficient Modelling Approach for an InP based Mach-Zehnder modulator," in 25th Irish Signals & Systems Conference and China-Ireland International Conference on Information and Communities Technologies (Institution of Engineering and Technology, 2014), pp. 123–128.

- G. L. Li, C. K. Sun, S. A. Pappert, et al., "Ultrahigh-speed traveling-wave electroabsorption modulator-design and analysis," IEEE Trans. Microwave Theory Tech. 47(7), 1177–1183 (1999).

- 32. S. Irmscher, Design, Fabrication and Analysis of InP-InGaAsP Traveling-wave Electro-absorption Modulators (Royal Institute of Technology, 2003).

- R. Lewen, S. Irmscher, and U. Eriksson, "Microwave CAD circuit modeling of traveling-wave electroabsorption modulator," IEEE Trans. Microwave Theory Tech. 51(4), 1117–1128 (2003).

- F. Fiedler and A. Schlachetzki, "Optical parameters of InP-based waveguides," Solid-State Electron. 30(1), 73–83 (1987).

- M. Sotoodeh, A. H. Khalid, and A. A. Rezazadeh, "Empirical low-field mobility model for III–V compounds applicable in device simulation codes," J. Appl. Phys. 87(6), 2890–2900 (2000).

- M. Levinshtein, S. Rumyantsev, and M. Shur, Handbook Series on Semiconductor Parameters (World Scientific, 1996), 1.

- 37. G. Ghione, Semiconductor Devices for High-Speed Optoelectronics (Cambridge University Press, 2009).

- 38. S. M. Sze and K. K. Ng, Physics of Semiconductor Devices (Wiley, 2006).

- 39. K. Kawano, K. Wakita, O. Mitomi, *et al.*, "Design of InGaAs-InAlAs multiple-quantum-well (MQW) optical modulators," IEEE J. Quantum Electron. **28**(1), 224–230 (1992).

- 40. G. Ghione and M. Pirola, Microwave Electronics (Cambridge University Press, 2017).

- S. E. Laux, "Techniques for Small-Signal Analysis of Semiconductor Devices," IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 4(4), 472–481 (1985).

- 42. Y. R. Kwon, V. M. Hietala, and K. S. Champlin, "Quasi-TEM Analysis of "Slow-Wave" Mode Propagation on Coplanar Microstructure MIS Transmission Lines," IEEE Trans. Microwave Theory Tech. 35(6), 545–551 (1987).

- 43. R. E. Collin, "Transmission Lines," in Field Theory of Guided Waves (IEEE, 2009), pp. 247–328.

- 44. W. Hilberg, "From Approximations to Exact Relations for Characteristic Impedances," IEEE Trans. Microwave Theory Tech. 17(5), 259–265 (1969).

- M. Y. Frankel, R. H. Voelker, and J. N. Hilfiker, "Coplanar transmission lines on thin substrates for high-speed low-loss propagation," IEEE Trans. Microwave Theory Tech. 42(3), 396–402 (1994).

- 46. S. Adachi, Properties of Group-IV, III-V and II-VI Semiconductors (Wiley, 2005).

- 47. K. Lawniczuk and M. K. Smit, "JePPIX: access to generic foundry processes for InP photonic integrated circuits," in *Avionics, Fiber-Optics and Photonics Technology Conference* (IEEE, 2014), pp. 43–44.

- 48. "JePPIX Platform for Photonic Integration Homepage," https://www.jeppix.eu/.

- I. Kim, M. R. T. Tan, and S.-Y. Wang, "Analysis of a new microwave low-loss and velocity-matched III-V transmission line for traveling-wave electrooptic modulators," J. Lightwave Technol. 8(5), 728–738 (1990).

- 50. W. Yao, G. Gilardi, M. Smit, et al., "Design and simulation of a series push-pull Mach-Zehnder modulator in a generic photonic integration platform," in Proceedings of the 19th Annual Symposium of the IEEE Photonics Benelux Chapter (2014).

- 51. J. A. Hillier, Q. Hu, H. Chen, et al., "A Co-planar Stripline Mach-Zehnder Modulator Enabling 160 GBd PAM-4 on an Indium Phosphide Platform," in Optical Fiber Communication Conference (Optica Publishing Group, 2024), paper Tu2D.4.

- L. M. Zhang and F. R. Kschischang, "Staircase Codes With 6% to 33% Overhead," J. Lightwave Technol. 32(10), 1999–2002 (2014).

- 53. J. Bolk, H. Ambrosius, R. Stabile, *et al.*, "Deep UV Lithography Process in Generic InP Integration for Arrayed Waveguide Gratings," IEEE Photonics Technol. Lett. **30**(13), 1222–1225 (2018).

- 54. R. Redd, M. A. Spak, J. P. Sagan, et al., Lithographic process for high-resolution metal lift-off, in W. Conley, ed. (1999), p. 1341.

- M. Zheng, Y. Yang, P. Liu, et al., "Fabrication of gold nanostructures using wet lift-off without adhesion promotion," Microelectron. Eng. 233, 111420 (2020).

- 56. JePPIX, "Unleashing the power of PIC Technology Roadmap 2021-2025," https://www.jeppix.eu/about-us/roadmap/.

- 57. R. Spickermann, S. R. Sakamoto, and N. Dagli, "In traveling wave modulators which velocity to match?" in 9th Annual Meeting Lasers and Electro-Optics Society (IEEE, n.d.), 2, pp. 97–98.