| MASTER                                       |

|----------------------------------------------|

| Energy models for network-on-chip components |

|                                              |

|                                              |

| Bhat, S.                                     |

| Award date:<br>2006                          |

|                                              |

| Link to publication                          |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 24. Mar. 2025

# **TECHNISCHE UNIVERSITEIT EINDHOVEN Department of Mathematics and Computer Science**

# ENERGY MODELS FOR NETWORK-ON-CHIP COMPONENTS

By Shubha Bhat

Supervisors: Dr. Ir. Twan Basten Dr. Ir. Marc Geilen

Ir. Sander Stuijk

# **ACKNOWLEDGEMENTS**

Foremost, I would like to thank my supervisor Dr. Ir. Twan Basten, Associate Professor at the Electrical Engineering department of the Technical University Eindhoven, Netherlands, for providing me with an opportunity to carry out my master thesis project at the department of electrical engineering at the university. I thank him for his support and encouragement throughout the project.

I also thank Dr. Ir. Marc Geilen, Assistant Professor at the Electrical Engineering department of the Technical University Eindhoven, Netherlands, for his valuable suggestions and ideas regarding my project during the discussions in the PROMES meetings.

I am especially grateful to Ir. Sander Stuijk, who guided me throughout the project and cleared all my doubts and questions patiently.

I would also like to thank all the PROMES group members, Dr. Ir. Bart Theelen, Amir Hossein Ghamarian, M.Sc. and Dr. Mohammad Mousavi, M.Sc. for their valuable suggestions throughout the project.

I thank my husband Aravind Bhat and our families back in India for giving me the support and encouragement throughout my study period.

Finally, I would like to thank all my colleagues at the electrical department and my friends for their love and support.

# A. ABSTRACT

Today with the advent of new VLSI processing technologies, System-on-Chip (SoC) design is gaining prominence in order to achieve faster time to market, reduced costs and flexible solutions. Present day embedded multimedia applications are becoming more computation intensive due to the large number of integrated functions .Often such applications are mapped onto mobile systems that need to operate with a low energy consumption.

It is seen that multiprocessor Systems-on-Chip (MPSoC) offer a superior performance and lower energy consumption than single processor systems. Networks-on-Chip (NoCs) are considered as an interconnection mechanism between the various IP blocks in an MPSoC. NoCs are preferred over traditional buses, as NoCs offer predictable timing behaviour and can easily scale without degrading the performance.

As modern systems are often mobile, energy consumption is an important design criterion. Therefore accurate estimates of the energy consumption of the implementation must be made early in the design process. This requires an energy model for various system components. Current state of the art energy estimation flows for MPSoCs take a path all the way to the low implementation levels taking into account all these low level details. During design-space exploration (DSE), it would be difficult to follow the entire time consuming flow for each potential solution. Hence, it is important to have abstract energy models of various components in the system and the system as a whole.

In this thesis, we focus on the NoC interconnect. We present energy models at an intermediate abstraction level for all NoC components in a typical SoC, namely links, FIFO buffers and routers and show how these models can be used to estimate the energy consumption of a complete NoC. The energy model of an individual component is expressed as a simple parameterized expression. These models are validated comprehensively by means of simulations carried out in MAGMA. The models can be used to compute the overall energy consumption for the communication part of the chip without carrying out time-consuming simulations. The abstraction level of the energy models is such that only a few parameter values need to be known. Examples are the frequency of changes in the incoming data and read and write rates. These parameters are application dependent and are less easily influenced by the designer. Also some of the architectural parameters such as FIFO sizes, flit size, number of input and output ports etc, that can be chosen by the designer, can be taken into account. Thus, the models are at a higher abstraction level than the gate and transistor level models used in MAGMA.

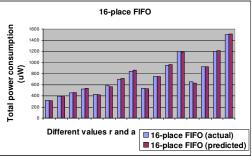

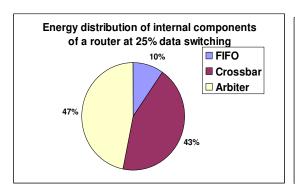

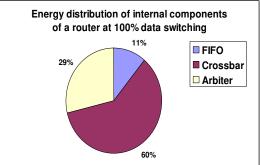

Our experiments on FIFO buffers exemplify that the energy consumption increases linearly with the number of FIFO places. Our results on router energy consumption show that the arbiter and the crossbar consume similar amounts of energy in the router. Furthermore, it is also seen that the energy consumed by the link doubles with doubling the link length. Our experiments suggest that, for a given fixed or average switching activity in the transferred data, the energy consumption is linear in the number of hops in the network, which is the commonly used abstract energy model for NoCs.

The work started in this thesis ultimately provides designers with concrete numbers concerning the power and energy consumption of SoCs enabling them to optimize their designs and perform trade-offs and take decisions through the predictions made based on the developed models preferably at an early stage in the design of a system.

# **B. TABLE OF CONTENTS**

| ACKN        | OWLE                 | DGEMENTS                                                    | 1           |

|-------------|----------------------|-------------------------------------------------------------|-------------|

| A. ABS      | TRAC                 | Γ                                                           | II          |

| B. TAB      | LE OF                | CONTENTS                                                    | III         |

| C. ABE      | BREVIA               | ATIONS                                                      | <b>v</b>    |

| D. LIS      | Γ OF F               | IGURES                                                      | VI          |

| E. LIST     | Γ OF T               | ABLES                                                       | VII         |

| F. LIST     | Γ OF PA              | ARAMETERS                                                   | VIII        |

| CHAP        | ΓER 1                | INTRODUCTION                                                | 1           |

| 1.1.        | Prob                 | LEM DEFINITION                                              | 1           |

| 1.2.        |                      | GY VS. POWER CONSUMPTION                                    |             |

| 1.3.        |                      | /ORKS-ON-CHIP                                               |             |

| 1.4.        | NoC                  | COMPONENTS                                                  | 3           |

| 1.5.        | GOAL                 | <i>z</i>                                                    | 3           |

| 1.6.        |                      | OACH AND CONTRIBUTION                                       |             |

| 1.7.        | THES                 | IS OVERVIEW                                                 | 4           |

| CHAP        | ΓER 2                | LITERATURE SURVEY OF POWER MODELS                           | 5           |

| 2.1.        | INTRO                | DDUCTION                                                    | 5           |

| 2.2.        | CLAS                 | SIFICATION OF POWER MODELS                                  | 5           |

| 2.2         | 2.1. Co              | mparison of OSI layers with NoCs                            | 6           |

| 2.2         | 2.2. <i>Co</i>       | mponent level                                               | 7           |

|             | 2.2.2.1.             | SoC and Application Models                                  |             |

|             | 2.2.2.2.<br>2.2.2.3. | Communication (NoC) Components                              |             |

|             | 2.2.2.4.             | Other Components                                            | 8           |

|             |                      | ferent levels of abstraction                                |             |

| 2.3.        | Conc                 | CLUSION                                                     | 10          |

| CHAP        | ΓER 3                | POWER MODEL FOR LINKS                                       | 12          |

| 3.1.        | INTRO                | DDUCTION                                                    | 12          |

| 3.2.        |                      | GY CONSUMPTION IN A WIRE                                    |             |

| 3.3.        |                      | ER EQUATIONS FOR A GATE DRIVEN WIRE                         |             |

| 3.3         | 3.1 Tro              | aditional ½ CV² Model to calculate the Dynamic Energy Consu | mption on a |

| Sir         |                      | e                                                           | -           |

| 3.3         | 3.2 Sta              | tic Power Consumption on a Single wire                      | 16          |

| 3.4         | Powe                 | ER EQUATIONS INCORPORATING CROSS-COUPLING EFFECTS           | 17          |

| 3.5         |                      | ER MODEL FOR A LINK                                         |             |

| CHAP'<br>19 |                      | DESIGN AND POWER MODEL OF REGISTER-BASE                     | D FIFOS     |

|             |                      |                                                             |             |

| 4.1.        |                      | DDUCTION                                                    |             |

| 4.2.        | IMPLI                | EMENTATION OF REGISTER BASED FIFO BUFFERS                   | 19          |

| 4.2.1 Implementation of 4-place FIFO Buffers                         | 19  |

|----------------------------------------------------------------------|-----|

| 4.2.2 Working of a 4-place FIFO buffer in terms of a behavioural FSM | 21  |

| 4.2.3 Alternate model of a FIFO buffer using shift registers         |     |

| 4.2.4 Pros and Cons of the above two architectures                   |     |

| 4.3. POWER MODEL FOR A FIFO                                          |     |

| 4.4. EXPERIMENTS AND RESULTS                                         |     |

| 4.4.1. Functional Verification of the model                          |     |

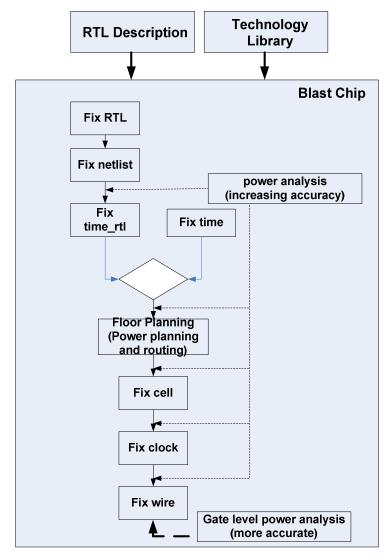

| 4.4.2 Power measurements and Power Analysis in MAGMA Blast Chip      |     |

| 4.4.3 Power measurements for the FIFO model in MAGMA                 | 25  |

| 4.4.3.1 Experiments for Measurement of Internal power                | 26  |

| 4.4.3.2 Experiments for Measurement of Leakage power                 | 29  |

| 4.4.3.3 Experiments for Measurement of switching power               | 31  |

| 4.4.3.5 Experiments for power measurement for different FIFO sizes   |     |

| 4.5. ANALYSIS OF FIFO POWER CONSUMPTION                              |     |

| CHAPTER 5 DESIGN AND ENERGY MODEL OF A ROUTER                        | 37  |

|                                                                      |     |

| 5.1. Introduction                                                    |     |

| 5.2. STATE OF THE ART OF ROUTERS                                     |     |

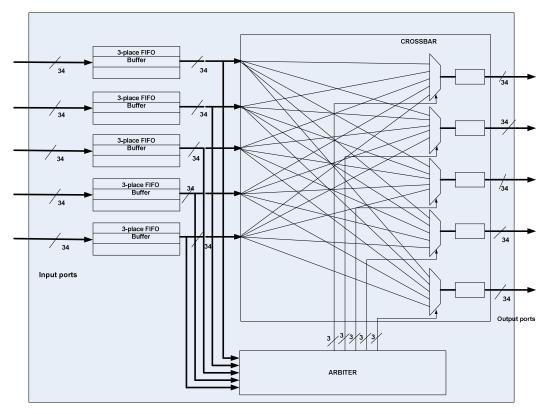

| 5.3. ROUTER ARCHITECTURE                                             |     |

| 5.4. ROUTER ENERGY MODEL                                             |     |

| 5.5. EXPERIMENTS FOR ENERGY MEASUREMENTS ON A ROUTER                 |     |

| 5.5.1. FIFO Energy model                                             | 42  |

| 5.5.2. Crossbar Energy Model                                         |     |

| 5.5.3. Arbiter Energy Model                                          | 42  |

| 5.5.4. Router Energy Model                                           | 43  |

| 5.6. ANALYSIS OF THE ENERGY MEASUREMENTS ON A ROUTER                 | 43  |

| CHAPTER 6 INTEGRATED ENERGY MODEL FOR ROUTERS, FIFOS                 | AND |

| LINKS 45                                                             |     |

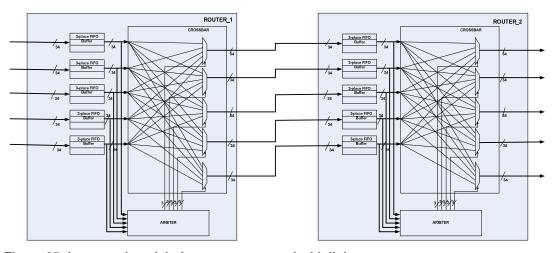

| 6.1. Integrated Model: Architecture                                  | 45  |

| 6.2. LINK ENERGY MODEL                                               | 45  |

| 6.3. COMPOSITIONAL ENERGY MODEL                                      | 46  |

| 6.4. Energy Measurements                                             | 46  |

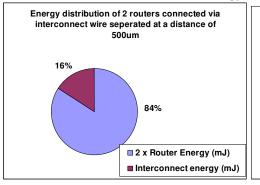

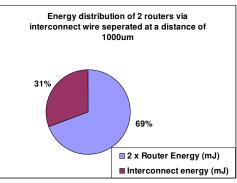

| 6.5. ENERGY DISTRIBUTION ANALYSIS                                    | 47  |

| 6.6. CONCRETE LINK MODEL                                             |     |

| 6.7. CONCRETE ENERGY MODEL FOR THE NOC AS A WHOLE                    |     |

| CHAPTER 7 CONCLUSION AND FUTURE RECOMMENDATION                       |     |

| CHAPTER / CUNCLUSION AND FUTURE RECOMMENDATION                       | 49  |

| REFERENCES                                                           | 50  |

# C. ABBREVIATIONS

ATM Asynchronous Transfer Mode

DRAM Dynamic Random Access Memory

CMOS Complementary Metal Oxide Semiconductor

CA Communication Assist

DSE Design Space Exploration

FIFO First in First out

FPGA Field Programmable Gate Array

FSM Finite State Machine IP Intellectual Property

ITRS International Technical Roadmap for Semiconductors

MPSoC Multiprocessor System-on-chip

MSE Mean Square Error NoC Network-on-chip

NMOS N-Channel Metal Oxide Semiconductor

OSI Open System Interconnect

PMOS P-Channel Metal Oxide Semiconductor

QoS Quality of Service

RTL Register Transfer Level

SoC System-on-chip

SRAM Static Random Access Memory

TDMA Time Division Multiple Access

VCD Value Change Dump

# D. LIST OF FIGURES

| Figure 1: Architectural template of a Multiprocessor SoC                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2: NoC with 3x3 mesh topology                                                                                                                                  |

| Figure 3: OSI layers with reference to Network-on-Chip components                                                                                                     |

| Figure 4: CMOS Circuit showing leakage current and reverse bias current                                                                                               |

| Figure 5: 2001, 2002 ITRS prediction of static and dynamic power consumption trends.13                                                                                |

| Figure 6: A simple interconnect wire model                                                                                                                            |

| Figure 7: CMOS Model of a Switching cell                                                                                                                              |

| Figure 8: 3 Interconnect wires with mutual capacitance                                                                                                                |

| Figure 9: 4-place FIFO buffer                                                                                                                                         |

| Figure 10: FSM of a 4-place FIFO buffer                                                                                                                               |

| Figure 11: FIFO model with shift registers                                                                                                                            |

| Figure 12: MAGMA Blast Chip design flow                                                                                                                               |

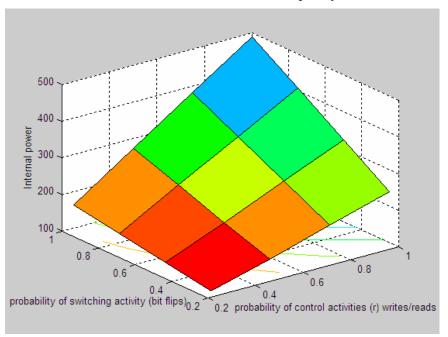

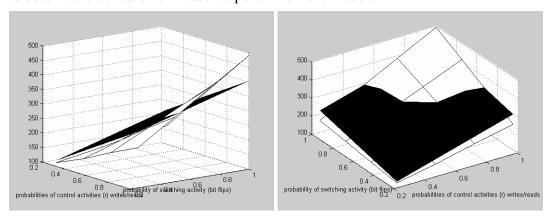

| Figure 13: 3D graph of internal power plotted against α and r for a 4-place FIFO at 500MHz28                                                                          |

| Figure 14: Overlapped 3D graph of actual (white) vs predicted (black) internal power against $\alpha_F$ and r for a 4-place FIFO at 500 MHz in two different angles28 |

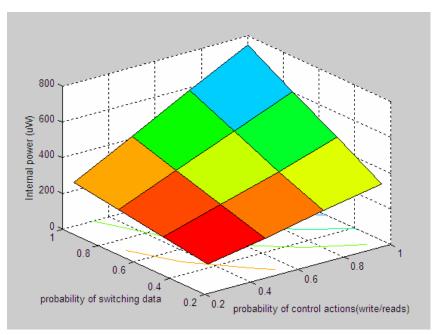

| Figure 15: 3D graph of internal power plotted against α and r for an 8-place FIFO at 500MHz                                                                           |

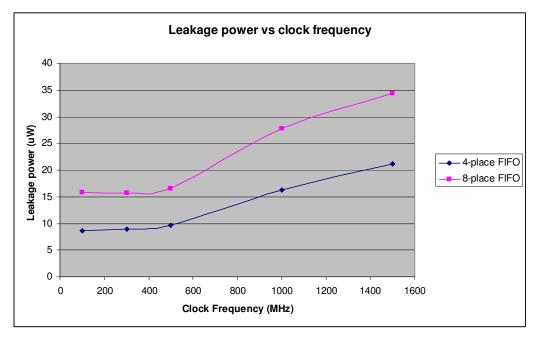

| Figure 16: Graph representing leakage power vs. clock frequency for a 4-place FIFO and an 8-place FIFO                                                                |

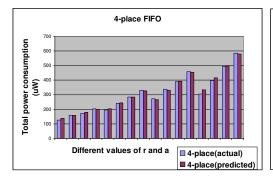

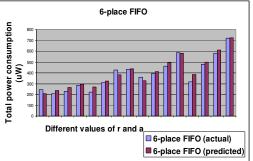

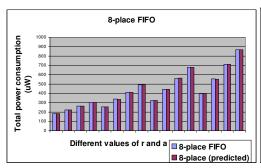

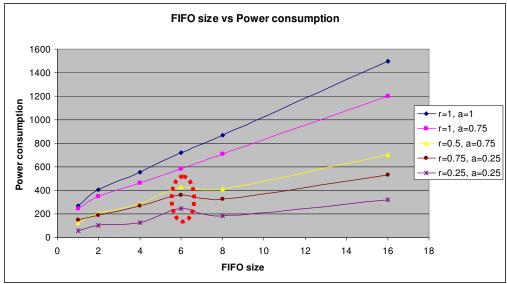

| Figure 17: Actual and predicted values of total power consumption for different values of r and a for different FIFO sizes                                            |

| Figure 18: Power consumption of different FIFO sizes35                                                                                                                |

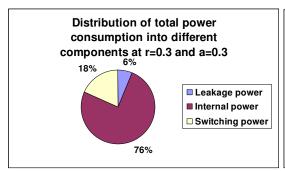

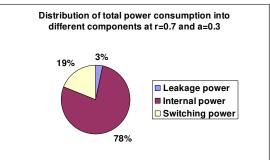

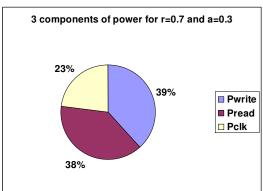

| Figure 19: Pie chart showing the distribution of different components of power with typical values of r and $\alpha_F$                                                |

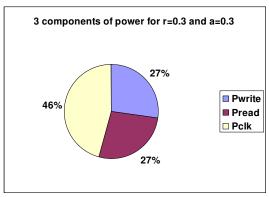

| Figure 20: Pie chart showing the three main components of switching power with typical values of r and $\alpha_F$                                                     |

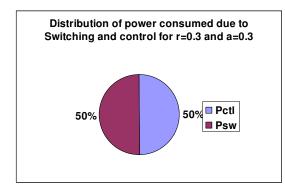

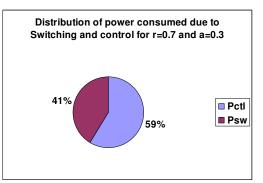

| Figure 21: Pie chart showing the switching and control component of power with typical values of r and $\alpha_F$                                                     |

| Figure 22: Router architecture40                                                                                                                                      |

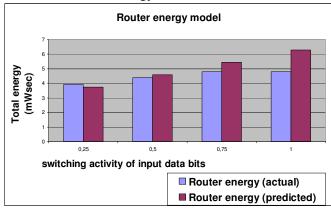

| Figure 23: Actual and Predicted values of energy numbers of a router for different values for r and a                                                                 |

| Figure 24: Pie chart of energy distribution for internal components of a router44                                                                                     |

| Figure 25: Integrated model of routers connected with links                                                                                                           |

| Figure 26: Energy distribution of the two routers put together vs link measured at two different distances                                                            |

# E. LIST OF TABLES

| Table 1: Classification based on comparison of OSI layers with NoCs7                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2: Classification based on component aspects9                                                                                                 |

| Table 3: Classification based on levels of abstraction                                                                                              |

| Table 4: Power numbers from MAGMA measurements against predicted numbers from the power model for the internal power @ 500 MHz of clock frequency27 |

| Table 5: Leakage power numbers against clock frequency for a 4-place FIFO29                                                                         |

| Table 6: Leakage power vs clock frequency for an 8-place FIFO buffer29                                                                              |

| Table 7: Power numbers from MAGMA measurements for switching power and leakage power for 4-place FIFO @ 500 MHz31                                   |

| Table 8: Actual and Predicted values for Power consumption due to write activity for a 4-place FIFO at 500MHz32                                     |

| Table 9: Actual and predicted power numbers for the total power consumption for a 4-size at 500 MHz33                                               |

| Table 10: Actual and Predicted values for total power consumption for a 4-place FIFO at 500MHz34                                                    |

| Table 11: State of the art NoC Routers                                                                                                              |

| Table 12: Power/Energy measurements of Router and its components@ 500MHz clock freq42                                                               |

| Table 13: Energy numbers for an integrated model with 2 routers at 50 MHz46                                                                         |

| Table 14: Energy numbers of integrated models with 2 and 3 routers at 100 MHz46                                                                     |

| Table 15: Energy numbers for Router and link at 100 MHz47                                                                                           |

# F. LIST OF PARAMETERS

C : Load Capacitance

V : Supply Voltage

f : Operating frequency

$\alpha_L$ : Link/wire switching activity, i.e., the number of 0 to 1 and 1 to 0

transitions per time unit, normalized by the clock frequency

$\alpha_c$  : Cross-coupling switching activity

$I_{short}$ : Short circuit current  $\tau$ : Short circuit period  $I_{bias, wire}$ : Reverse-bias current  $I_{leak, gate}$ : Leakage current

N : Number of wires in a link

$n_r$  : Number of routers

$P_{Link}$ : Link Power

$\alpha_F$ : bit flips in FIFO data

r : Rate of read and write actions n : Number of FIFO places

# Chapter 1 **Introduction**

### 1.1. Problem Definition

With technology scaling downwards, SoCs are getting more complex with additional power, area and speed constraints incorporating several processing components in a single chip. Today embedded multimedia applications are becoming more computation intensive due to the large number of functions incorporated within them. Often such applications are mapped onto mobile systems that are typically battery operated and support a wide range of applications so they have to be flexible as well as energy-efficient.

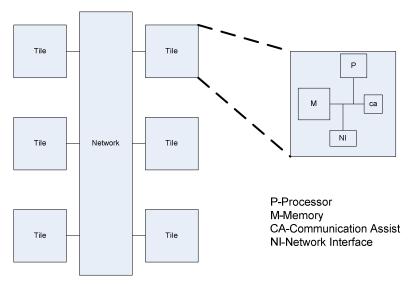

It is seen that multiprocessor Systems-on-Chip (MPSoC) offer a superior performance and lower energy consumption than single processor systems. A certain computational task accomplished by a single processor at a certain frequency can be achieved by multiprocessors in parallel with reduced frequency and voltage and thereby reduced energy consumption at the same amount of time. Figure 1 depicts a tile-based MPSoC. A tile normally is composed of a processor, a memory unit, communication assist and a network interface. A communication assist is a small controller that performs buffer accesses on behalf of the network. Most importantly, it decouples computation from communication.

For such systems, energy consumption is an important design criterion. Hence accurate estimates of the energy consumption of the implementation must be made early in the design process. This requires an energy model for various components in the system.

Figure 1: Architectural template of a Multiprocessor SoC

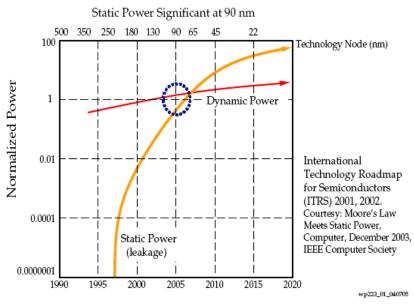

Total energy consumption is basically composed of two main components namely, the dynamic and the static or the leakage power. It is assumed that the leakage power will dominate the dynamic power consumption for technologies below 90nm (ITRS Roadmap, 2001-2002, Figure 5). Additionally, current applications are becoming more computation intensive and therefore more functions are added to the current systems. These increased computational requirements have led to the integration of multiple components on a chip operating at higher clock frequencies which has consequently resulted in the increase of overall energy consumption. Nevertheless, irrespective of the technology, it is necessary to have a prior knowledge of the total energy consumption on a chip.

This information can be used during the design to minimise energy consumption or to make trade-offs with other aspects. Information about energy consumption needs to be available in the form of parameterised models. Such models provide a basis to optimize energy consumption of SoC components and to set the parameters of the design of a SoC.

Further, the current state of the art flow takes a path all the way to the low implementation levels taking into account all the low level details. During DSE, it wouldn't be ideal to follow the entire flow for each instance. Hence, it is important to have abstract but accurate energy models for the various components in the system.

# 1.2. Energy vs. Power consumption

The term 'Power consumption' refers to the rate at which energy is consumed over time.. The term 'Energy consumption' is often of interest in the case of portable devices operated by battery. In such devices, the amount of energy needed to perform a computation is a more useful measure than the power consumption.

Consider two cases, one with high power consumption and another with low power consumption. Both these approaches require the same amount of energy to complete some operation. The solution requiring high power would simply be faster than the other.

Hence in this thesis, when referring to power consumption, it means power consumed at one moment in time, whereas energy consumption means the energy consumed over a period of time, typically for some given task or operation.

# 1.3. Networks-on-chip

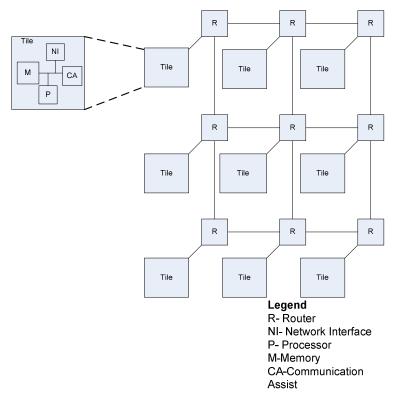

A Network-on-chip (NoC) is an efficient on-chip communication architecture for System-on-Chip architectures. It enables integration of a large number of computational and storage blocks on a single chip. Traditionally communication between processing elements was based on buses. But for large multiprocessor SoCs with many processing elements, it is expected that the bus will become a bottleneck from a performance, scalability and energy point of view [41][43]. Therefore the idea of networks on chip has evolved which consists of a set of routers interconnected by links. Figure 2 shows a typical 3x3 mesh topology with each network interface connecting one IP to a router.

End to end communication between IP blocks is accomplished by the exchange of messages. These messages are further broken down into packets. Packets are the standard form of representing the information for communication. Packets are split into several flits, which is the basic unit of data transfer in a NoC.

There are two main parts of the interconnection network, the services and the communication system. A typical service is a bidirectional communication channel with reserved bandwidth that offer throughput and latency guarantees. The communication system is what supports the transfer of information from source to destination in the NoC structure or the network topology. A routing algorithm determines the route of a packet from source to destination.

Figure 2: NoC with 3x3 mesh topology

# 1.4. NoC Components

A typical NoC (Figure 2) is composed of multiple routers and network interfaces (NI) which connects the IP blocks to the network. Each tile is composed of a processor, communication assist (CA), memory and a network interface as mentioned in the previous section. Routers and NIs are connected through links. A router routes the packets along the network. A network interface makes the IP view (protocol) compatible to the router view on communication (packets). Each NI can connect multiple IP blocks to the router network. Each router is composed of FIFO buffers, an arbiter and a crossbar to route the packets to the destination. FIFOs are also available in the NI. In this thesis, we will therefore focus on FIFOs, routers and links.

# 1.5. Goal

The main goal of this thesis is to develop energy models for Network-on-Chip (NoC) components that characterize the energy consumption of these systems and their components. These models should allow the prediction of the energy consumption of NoC-based systems. To achieve this goal, it is necessary to investigate and profile the energy consumption of various processing, communication and storage components that form a part of NoC-based systems. In order to estimate the energy consumed by components in isolation, we need to build energy models and analyze the different parameters that contribute to the overall energy consumption of the component. Therefore, the resulting model thus developed will allow designers to predict the energy consumed by these components. As mentioned, this thesis focuses on models for routers, FIFOs and interconnecting links.

Several power and energy models have been proposed by different people from the SoC community, each focusing on a specific issue. It is necessary to get an in-depth knowledge of these traditional energy models through an extensive literature study. Through this literature study, it is intended to answer and analyze several questions such as those concerning the level of abstraction dealt with while estimating energy consumption of individual components, the correctness of models in terms of relative and absolute accuracy and their impact on a system as a whole.

# 1.6. Approach and Contribution

With reference to the goal mentioned in Section 1.5, NoC components are designed and implemented in Verilog at RT level and thereafter energy models of these components are built. Energy and power measurements are then carried out on these designs to validate the models.

Initially the existing analytical model of a link is reviewed as in the literature. However a concrete energy model for the link is given only at the time of developing a compositional energy model for an entire NoC. Further, an n-place FIFO is designed and an abstract energy model is proposed for the same comprising several architectural and application specific parameters. The same procedure is followed to develop an abstract model for the router and its components in isolation. Finally a compositional energy model of the whole NoC is developed.

Therefore to summarise, in the current thesis, energy models for NoC components are built at a higher level of abstraction, i.e, at the transaction level. It is further intended as a future work that energy models for computational components also be developed and integrated with the NoC components to build models for the SoC as a whole.

# 1.7. Thesis Overview

The thesis is organized as follows. In Chapter 2, a literature survey of energy and power models is done with references to the literature and resulting in a classification of energy and power models based on various criteria. Chapter 3 deals with the energy model of the links; however at this stage only a mathematical model for the links is specified and this is validated after implementing the routers which act as realistic input and output blocks connected via an interconnecting link. Chapter 4 deals with the design and energy model of FIFO buffers along with experimental results. Chapter 5 explains the energy model of a router along with the experimental results. Chapter 1 deals with a compositional energy model that integrates all NoC components explained in the previous chapters. Chapter 1 summarizes the conclusion of the thesis together with the ideas for future recommendations.

# Chapter 2 Literature Survey of Power Models

# 2.1. Introduction

There has always been a need to estimate and analyse the power consumption on a chip in order to optimise the chip design for energy consumption or to map applications onto systems to achieve low power. With this objective, power models are developed at various abstraction levels for SoCs and especially for NoC-based SoCs.

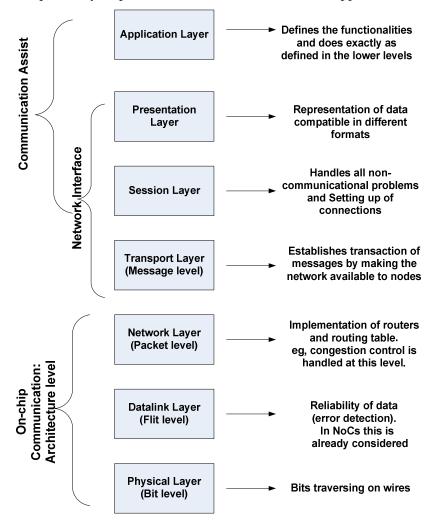

The concept of networks-on-chip is often compared with that of the fundamental concepts of communication networks and more specifically with the OSI seven layer model [2][4]. Figure 3 depicts the seven layers and their respective importance in the field of NoCs. More specifically for a NoC architecture, the last four layers are very important. Therefore, we can classify NoCs in terms of the OSI layers.

Secondly, at the lowest level of abstraction, bits of data are sent through links (bunch of wires) from one processing node to another via intermediate routers. Here, the energy consumed is the sum of the energy consumed by the links (through the wires), nodes (processing elements) and intermediate routers which in turn include the power consumed by internal components such as buffers, arbiters and crossbars during switching action.

At higher levels, energy consumed due to the sending of one bit of data from one router to another via the links is a function of the number of hops (or the number of routers) and the number of links. The energy consumed by the bit is given by:

$$E_{bit} = n_{routers} * E_{router} + n_{links} * E_{link}$$

This is typical to networks where a router is connected to each processing element.

Thus, energy models are dealt with at different abstraction levels normally focusing on the application and at times focusing on the architecture. It is often challenging or simply impossible to take into consideration all these aspects and abstraction levels; however a reasonable compromise can lead to efficient models.

In this chapter, details concerning the classification of energy models at various levels of abstraction and at various component levels are studied together with some related work done by different people. Three different tabular representations of the classifications along with the references are made so as to locate the references common to all the three classifications (shown in section 2.2), thereby investigating the development of energy models at different levels and focusing at different aspects. We also identify those energy models that focus on one particular area.

# 2.2. Classification of Power Models

In this section, a classification of Power/Energy models is made based on three essential categories. They are as follows:

- 1. Comparison of OSI layers with NoCs.

- 2. Component level

- a. Communication elements

- i. Routers

- ii. Links

- b. Computational elements

- i. Processors-Instruction level

- ii. Memories

- c. Other devices

- i. Peripherals

- ii. I/O interfaces

- 3. Different levels of abstraction

- a. Algorithms (Functionalities)

- b. Transaction level

- c. Register transfer level

- d. Gate level

- e. Transistor level

# 2.2.1. Comparison of OSI layers with NoCs

Figure 3 below depicts the seven OSI layers [3][4] and their comparison with on-chip communication. The level of depth and accuracy increases as we move towards the physical layer. The lower three layers are concerned with the architecture of the network while the top four layers provide communication services to applications.

Figure 3: OSI layers with reference to Network-on-Chip components

Table 1 shows the classification of NoCs when compared to the OSI layers with references. In the table, we observe that most models focus on the lower levels. No work is done on the higher levels, because most of the network related issues are handled at low levels, while the top three layers are more concerned with the application and the operating system in general. Therefore no power models are developed in this area.

| OSI seven layers                                  | References                                                                   |

|---------------------------------------------------|------------------------------------------------------------------------------|

| Application layer                                 | -                                                                            |

| Presentation layer                                | -                                                                            |

| Session layer                                     | -                                                                            |

| Transport layer (messages) - packetization issues | [15] – network power model based on message flows injected into the network. |

| Network layer (packets)                           | [5] – Packet switching fabrics,                                              |

| Datalink layer (flits)                            | [15] – modelling based on flits traversing in a link.                        |

| Physical layer (bit level)                        | [1],[6],[7]                                                                  |

Table 1: Classification based on comparison of OSI layers with NoCs

### 2.2.2. Component level

We can broadly distinguish the components on a chip into three classes. They are communicational or NoC components, computational elements and other additional devices. Further in this classification we illustrate some references that describe power models for the system as a whole. We define a system as a collective whole of many subcomponents including system software, whereas the application is treated separately. Table 2 provides the classification, discussed in more detail below.

# 2.2.2.1. SoC and Application Models

Energy models at this level are built considering the SoC as a whole. In [9], they used cycle accurate power models for an audio decoder application and in general their focus was on energy optimization for multimedia applications and device drivers again dealing at low level. The power models of some of the components were developed from the datasheets of the same obtained from the manufacturers. To deal with other SoC components, they used the validated power models developed by other authors. In [45], a cycle accurate multiprocessor System-on-Chip power simulation platform called GRAPES was developed.

In [15], a comparison of various benchmark applications based on their power consumption was made.

### 2.2.2.2. Communication (NoC) Components

At this level, energy models are built for various NoC components [1] such as links, buffers, routers, arbiters and controllers.

In [1], the authors performed experiments on register transfer (RT) level models to carry out trade-off analysis between the amount of power consumed by various components

versus performance parameters such as injection rate of packets into the network, the number of virtual channels. In [1], the power models were dealt with at a low level of abstraction i.e., at gate level and hence focussed on issues concerning both dynamic and leakage power consumption.

In [5],[6] and [7], energy models were developed on various cross-bar based routers. The starting point of their experiments was based on extensive analysis carried out to study the power consumption on routers. While [15] was more related to power models for links.

### 2.2.2.3. Computational elements

In [8], the work focuses on different register architectures in order to obtain low cost solutions especially in media processing applications without degrading the performance at transistor level. They focussed on different register architectures in order to obtain low cost solutions especially in media processing applications without degrading the performance.

In [11], the authors claimed that significant power savings can be achieved using various optimization techniques particularly on processors at the instruction level (concerning the number and type of instructions executed). They established that techniques such as datacode transformation and hence the number of instructions (measured as current drawn by individual instructions, [12]) have significant impact on processor power consumption.

In [13] and [14], the authors also dealt with power models at instruction level where they redefined the claim made by [12] that stated that total power consumption was the sum (function of current drawn) of all the instructions. They ([13] and [14]) proved that the power consumption was due to the circuit changes between consecutive executed instructions and this information needs to be taken into account in particular to establish accuracy.

In [10], the authors propose high-level analytical power models (for both on-chip and off-chip components) with FPGA-based co-processors achieving reasonable accuracy ( $\approx$ 12%). They mainly focussed on input-output traffic between local memory and processing elements.

### 2.2.2.4. Other Components

Apart from NoC and computational components, focus has been on other SoC components such as peripheral devices. Profiling the power-consuming components is a basis to this approach.

In [9], the work was focussed around power models for components such as device drivers at cycle accurate level. The power models of some of the components were developed from the datasheets of the same obtained from the manufacturers.

| Components                    |                                              |                                                 |                                                                                                                                      |                                      |

|-------------------------------|----------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| SoC<br>(System as<br>a whole) | Application                                  | Communication elements NoC                      | Computational elements                                                                                                               | other                                |

| [9], [45]                     | [15] – Comparison of benchmark applications. | [1] - Physical<br>links and routers             | [8]- Registers for processors                                                                                                        | [9] -<br>audio &<br>video<br>devices |

|                               | [8]- Media processing applications.          | [5] – Routers                                   | [10]-Processors at<br>Instruction level (loop<br>transformation);<br>Memory models<br>developed based on its<br>internal parameters. |                                      |

|                               |                                              | [6] – Routers and interconnection architectures | [11] – Processors:<br>Data reuse<br>transformation at<br>instruction level                                                           |                                      |

|                               |                                              | [7] – Routers & links                           | [12] – Processors: at instruction level.                                                                                             |                                      |

|                               |                                              | [15] – link utilization.                        | <ul><li>[13] – Processors at instruction level based on switching actions.</li><li>[14] – Same as [13].</li></ul>                    |                                      |

**Table 2: Classification based on component aspects**

### 2.2.3. Different levels of abstraction

Energy models are also classified based on different levels of abstraction. At the highest level of abstraction is the algorithm level with different functions and processes. This level emulates the functionalities performed at the lower levels. Subsequent to this is the transaction level, where processes correspond to events. Each write or read transaction is considered as an event and do not go into details up to the register transfer level. The models at these two levels represent the system level and are less accurate but also require less simulation time. The next level lower in the abstraction is the register transfer level. The transfer of data is at register and wire level, but does not deal further to gate or transistor level. The models at this level are very accurate but need more time to simulate. Next to this level are the transistor or gate levels which represent the model at circuit level and are more accurate than any of the other levels; however these models are extremely timing consuming.

In [7], energy models were developed based on an appropriate algorithm that mapped a given IP to a regular network architecture which is deterministic and deadlock-free using worm-hole routing.

At transaction level, energy models are dealt with at a system level and principally without going into the hardware details of individual components. In [5], power models were

developed aiming at a low power NoC solution and observing the system performance on shared memory ATM based switch fabrics. Further, they emphasized the importance of moving power optimization processes from circuit level to system level.

In [6], transaction level power models were developed for various cross-bar based routers. The starting point of the experiments was based on extensive analysis carried out to study the power consumption of routers. Both [5] and [6] deal with the transaction level and focus only on dynamic power consumption and neglect leakage power. The main reason for this was due to the complexity involved in computing the leakage power. Secondly, the processing technology employed made it possible to neglect the leakage component. Most importantly, they aimed at improving performance metrics such as throughput and delay at system level.

In [11],[12],[13] and [14] energy models were developed for processors at instruction level. They measured the power consumed by individual instructions as the current drawn by each instruction along with the impact caused by circuit changes due to the execution of consecutive instructions.

In [45], a Multiprocessor Systems on-Chip power simulation platform called GRAPES was developed at cycle accurate level. Several optimization techniques of the synchronization mechanism for MPSoC based NoC were explored.

In [1], power models were developed at the Register transfer level to carry out trade-off analysis between power consumed by various components and parameters such as size of packet, length and width of physical links, number and depth of virtual channels and switching technique.

| Level of Abstraction              | References       |

|-----------------------------------|------------------|

| Algorithm level (functionalities) | [7]              |

| Instruction level                 | [11][12][13][14] |

| Cycle Accurate level              | [45]             |

| Transaction level                 | [5],[6],[15]     |

| Register transfer level           | [1]              |

| Gate level                        | [9]              |

| Transistor level                  | [8]              |

Table 3: Classification based on levels of abstraction

# 2.3. Conclusion

We can thus infer from the above description that power models are developed at various levels of abstraction and targeted for particular components that are communicational or computational. Based on these models, predictions of power consumption are made in order to optimise systems and to map applications onto systems to achieve low power.

From the literature study it was observed that some of the energy and power models are too low level (e.g. transistor level) and are also too expensive and time consuming to evaluate, while some of them are too abstract and are not accurate enough. Some power models describe only one or a few components of a SoC which are not usable for the SoC design as

a whole. Therefore, we intend to target an intermediate level of abstraction that leads to models usable for the evaluation of the SoC as a whole during architectural design space exploration.

In this thesis, NoC components are designed and implemented at Register transfer level, which is at a low level. However the energy models are developed at a higher abstraction level than the RT level and to be precise, they are represented at transaction level. It is further intended as a future work that energy models for computational components also be developed and integrated with the NoC components to build models for the SoC as a whole.

# Chapter 3 **Power Model for Links**

# 3.1. Introduction

We are aware of the fact that the evolution of Multiprocessor System-on-chip (SoC) designs have resulted in a number of NoC-based interconnect architectures [6][18][21]. These aim to achieve an improved communication system compared to the traditional architectures in terms of energy consumed, throughput and latency. On the other hand, current technologies are migrating towards achieving smaller device sizes and shortened interconnects. However, these short interconnects are posing a serious threat in achieving low power solutions in terms of additional heat dissipated on the system due to the decreased spacing between the wires and increased load on the wires due to increased frequencies. Therefore, in this chapter, we analyze the different issues concerning the power consumed in the interconnect wire by means of a detailed study of power models. These models can not only give us an insight in how power models are developed in general but can also help us in identifying the key parameters responsible for the power consumption of the wires in a chip.

# 3.2. Energy Consumption in a Wire

In order to calculate the energy consumed in an interconnect wire we need to study its analog or electrical behavior. In a wire, significant energy is consumed during the switching activity (charging and discharging) of the capacitor, which is normally referred to as the switching power. However, a portion of energy is also consumed as a result of a short circuit during switching activity at the driving gate's output; this is referred to as internal power. Both of these together form the dynamic energy. This contributes to about 70-90% of the total energy consumption under normal operating conditions. While a portion of energy is lost due to the leakage power irrespective of the switching activity and state of the gate [19], this is referred to as the static energy. The static component contributes to about 10-30% of the total energy consumption.

At processing technologies until 90 nm, it has been seen that dynamic power is the major power consuming component [23] (refer Figure 5) but at technologies below 90nm, this leakage power begins to build up, due to the fact that at lower technologies the supply voltage and thereby the threshold voltage is also reduced consequently. This definitely reduces the dynamic power consumed but on the other hand the static power increases due to the increased leakage currents from the non-conducting gates flowing from source to ground which is more prominent with dropping voltages due to its exponential dependency on threshold voltage [24]. As a result, the power consumptions due to the leakage current are increased.

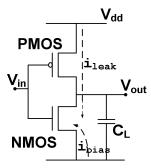

Figure 4: CMOS Circuit showing leakage current and reverse bias current

In order to understand the dynamic and static energy components more precisely, they will be dealt with in detail in section 3.3 focusing on a single interconnect wire.

In addition to the above mentioned components of power consumption, when we consider a larger interconnect system such as a NoC with wires adjacent to each other (owing to their physical routing scheme), energy is consumed due to cross-coupling and self coupling effects [17],[22]. The former is caused by interference of activities between the neighboring wires while the latter is caused by interference between different events on the same wire. The coupling capacitance in particular is significant with shrinking technologies. Due to the decreased spacing between wires, the cross coupling capacitances are increased thereby increasing the power consumption. Hence we will focus on the cross coupling effects in section 3.4 In section 3.5, the total power consumption of a link will be calculated.

Figure 5: 2001, 2002 ITRS prediction of static and dynamic power consumption trends

# 3.3. Power equations for a gate driven wire

As mentioned in the earlier section, power consumption in a gate driven interconnect wire is a combination of dynamic and static power.

$$P = \frac{1}{2}C_LV^2\alpha_L f + \tau\alpha_LVI_{short}f + VI_{bias, wire} + VI_{leak, gate}$$

Here the first component is the dynamic power consumption caused by charging and discharging of capacitive load on the gate's output where ' $C_L$ ' is the load capacitance, 'V' is the supply voltage, ' $\alpha_L$ ' is the switching activity of the gate and f is the operating frequency of the system. Switching activity is defined as the number of 0 to 1 and 1 to 0 transitions, normalized by the operating frequency. The switching activity constant eventually captures the above mentioned self-coupling effect.

The second component is also a part of the dynamic power consumed by a momentary short circuit caused between supply and ground when the gate's output is switching, Figure 7. Here  $\tau$  is the short time period during which the short circuit current  $I_{short}$  flows between source and ground.

The third component is the static power consumed when there is no switching activity and specifically as a result of the circuit structure, the wire, [25] and  $I_{bias, wire}$  is the current flowing from the wire to its substrate (irrespective of the gate).

The fourth component, also a part of the static power, is the leakage power consumed by the gate due to the leakage current flowing again from source to ground but regardless of the gate's state and switching activity.

Finally, note that the capacitance and current constants in the above model depend on the length of the wire, i.e., the above model implicitly gives the power dissipation of a wire per unit length.

# 3.3.1Traditional ½ CV<sup>2</sup> Model to calculate the Dynamic Energy Consumption on a Single wire

The  $\frac{1}{2}CV^2$  model [22] has been used commonly to measure the interconnect energy consumption. This model is based on the assumption that energy is consumed in every rise or fall transition of an event [20]. In this model we concentrate only on a single wire and neglect the coupling effect caused by the neighboring wires. The effect of coupling capacitors will be dealt with in section 3.4. Further, in this model, we also neglect the effect of resistance, assuming that the capacitor requires sufficiently long time to charge. The energy consumed by the wire during one transition from low to high and back (during charging and discharging of the capacitance) is given by  $E = C_L V^2_{dd}$ , where  $C_L$  is the total load capacitance and  $V_{dd}$  is the supply voltage. This can be derived as follows.

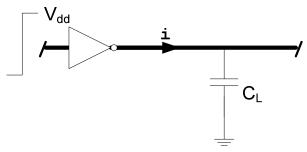

Consider a simple interconnect wire model as shown in Figure 6 with a load capacitance  $C_L$  which is the sum of the wire capacitance  $C_{wire}$  and the capacitance of the input gate, an inverter driving the wire. The two gates is a combination of PMOS and CMOS transistors as shown in the Figure 7.

Figure 6: A simple interconnect wire model

Figure 7: CMOS Model of an inverter cell depicting switching power (left) and internal power (right)

When the voltage at the input switches from low to high i.e., from 0 to  $V_{dd}$ , the capacitor gets charged from 0 to  $V_{dd}$  in T amount of time (this T can be assumed sufficiently large). Here we assume a zero rise and fall time, which means switching between low to high or vice versa is instantaneous and ideally the transistors in the driving gate are never ON at the same time. During the transition from low to high, the current i flows from the power supply to the capacitor via the PMOS transistor. The energy consumed from the power supply during this transition can be calculated as follows:

The power consumed during low to high transition is given by:

$$P(t) = i(t)V_{dd}$$

,

Where  $V_{dd}$  is the supply voltage needed to charge the capacitor from 0 to  $V_{dd}$  and i is the current drawn from the power supply to charge the capacitor. P and i both depend on the time t. The current i equals:

$$i(t) = C_L \frac{dV_{out}}{dt}$$

The energy that is drawn from the power supply can be derived as follows:

$$E_{0->1} = \int_{0}^{T} P(t)dt = \int_{0}^{T} i(t)V_{dd} \cdot dt$$

$$= C_{L}V_{dd} \int_{0}^{T} \frac{dV_{out}}{dt} dt$$

$$= C_{L}V_{dd} \int_{0}^{V} dV_{out}$$

$$= C_{L}V_{dd}^{2}$$

Also the energy stored in a capacitor can be calculated as follows:

$$E_{capacitor} = \int_{0}^{T} i(t) \cdot V_{out} \cdot dt = \int_{0}^{T} C_{L} \frac{dV_{out}}{dt} V_{out} dt$$

$$= C_{L} \int_{0}^{V_{out}} V_{out} \cdot dV_{out}.$$

$$= \frac{1}{2} C_{L} V_{dd}^{2}$$

From the above equation, we can say that only half of the energy is used to charge the capacitor during low to high transition. The other half of the energy is dissipated by the PMOS transistor. During transition from high to low, no energy is drawn from the supply and the capacitor discharges its energy into the NMOS transistor. Thus, the total amount of energy drawn from the power supply during both the transitions together (switching activities) equals  $C_L V_{dd}^2$  and  $1/2 C_L V_{dd}^2$  on average per transition.

In general, we also need to take into account how often the circuit switches. For simplicity, from now on,  $V_{dd}$  will be replaced by V. Thus the switching power is given

by

$$P_{switching} = \frac{1}{2} \alpha_L C_L V^2 f$$

, which is the first component in the formula given in section 3.3.

This can be captured in a constant  $\alpha_L$ , which is called the switching factor and has a value between 0 to 1 representing the switching activity relative to the clock frequency f. Thus by knowing how often a circuit is switched, we may calculate the total power consumed in a wire.

While deriving the power equations in an interconnect we assumed that the switching between low to high and vice versa happens instantaneously. This is an ideal situation. But in reality, this never happens and there is always a sloping transition from low to high and vice versa. During this period, there is a small leakage current flowing from the source to ground, when the outputs of the gates are switching. At one moment both the transistors in the driving gate are conducting and this short-circuit current flows until a stable condition is reached. This gives the following component in the equation of section 3.3

$$P_{short} = \tau \alpha_L V I_{short} f$$

,

where  $\tau$  is the short period during which this leakage occurs and  $I_{short}$  is the short circuit current flowing from source to ground.

# 3.3.2Static Power Consumption on a Single wire

Static power is the power dissipated by a gate or a wire when it is inactive or in static state. The static power is mostly influenced by the structure of the circuit. Ideally the static current of the CMOS circuit is equal to zero as the NMOS and PMOS devices are never on simultaneously in steady-state operation. But, a leakage current flowing through the reverse biased junctions of the transistor, located between the source and the ground causes the static power dissipation. When voltage falls below a certain threshold voltage, these static powers are consumed which prevent the gate from completely turning off. This power is drawn from the supply and more specific from the battery when referring to hand-held devices. Also, static power is dissipated when current leaks between the diffusion layers and the substrate. The static power dissipation can be express by the equation:

$$P_{static} = VI_{bias, wire} + VI_{leak, gate}$$

.

The leakage power is thus assumed to be a serious threat at technologies below 90nm, due to reduced threshold voltages.

# 3.4 Power Equations incorporating Cross-Coupling effects

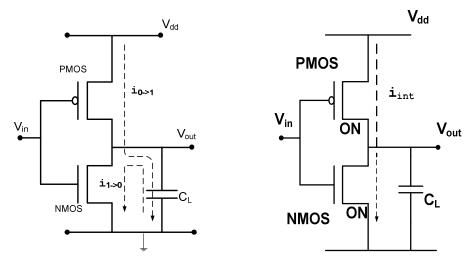

Figure 8 shows a simple interconnect model comprising three wires with their respective load capacitance and in addition a mutual (cross) capacitance between the wires. This cross coupling capacitance results in increased consumption of power. The effect due to this cross capacitance is often termed cross-talk.

This cross-talk effect is prominently seen when the wires are switching to different output values and when one of the two wires switches, while the other doesn't and both have different output values.

The power model for a 3-wire interconnect and therefore in general for an N-wire interconnect can be derived as follows.

Consider a 3-wire interconnect as shown in Figure 8 with  $C_C$  the cross coupling capacitance with a relative switching activity  $\alpha_C$  between wires. In order to study the impact of cross-coupling, we must also take into account the self capacitance which is the result of switching activity within the wire. This is necessary due to the fact that cross coupling occurs as a result of opposite switching activities between the adjacent wires. Let  $C_L$  be the load capacitance and  $\alpha_L$  the switching activity caused due to switching within the wire.

Here we choose three wires because mutual coupling can be better understood with three wires as we can focus on the middle wire with mutual coupling effect separated by a distance 'd' from its two adjacent neighbors. The capacitance on the middle wire is  $C = C_L + 2C_C$ , where  $C_L$  is its (middle wire) load capacitance and  $2C_C$  is the coupling capacitance of both the neighboring wires. From the equation above it appears as if the coupling effect is dominating over the self coupling capacitance. However, when considering the total power consumption due to transitions on all the three wires as a link, we notice the following:

$$C_{total} = 3C_L + 2C_C$$

And therefore in general for an N-wire interconnect, we obtain  $C_{total} = NC_L + (N-1)C_C$

Therefore knowing the total capacitance including cross-coupling and self-coupling of a link, ignoring the static power and the effect caused by the momentary short-circuit for the current discussion, we obtain the power equations for N wires as shown below:

$$P_{switching} = \frac{1}{2} (NC_L \alpha_L + (N-1)C_C \alpha_C) f V^2$$

Assuming N≈N-1 for a large interconnect, we obtain

$$P_{switching} \cong \frac{1}{2}N(C_L\alpha_L + C_C\alpha_C)fV^2$$

From the equations above, it is obvious that the coupling effect cannot be neglected if Cc is large. Now, the important thing to analyse is how large is  $C_C$  with respect to  $C_L$ . From the studies performed by [17] on a 0.25 $\mu$ m process technology, it is observed that the values of  $C_L$  are two or three times the values of  $C_C$  for a distance of say 1 $\mu$ m separating the wires. So assuming equal  $\alpha_L$  and  $\alpha_C$ , the cross-coupling effect is responsible for 25-33% of the

switching power. When moving towards  $0.09\mu m$  or 90nm technology and the typical values of distances separating the wires are reducing below  $1\mu m$  (current trend  $0.2\mu m$ ) and for such distances, the typical values of  $C_C$  are much more than  $C_L$  (factor of 2 or 3). This gives an indication of the threat due to coupling capacitance for the future technologies.

Figure 8: 3 Interconnect wires with mutual capacitance

### 3.5 Power model for a link

From the power models derived in section 3.3 for a single wire and the power model considering the cross-coupling effect for N-wire interconnect in section 3.4, we may conclude the total power for an N-wire link per unit length as follows:

$$P_{link} = \frac{1}{2}NV^{2}(C_{L}\alpha_{L} + C_{C}\alpha_{C})f + N\tau\alpha_{L}VI_{short}.f + N.(VI_{bias, wire} + VI_{leak, gate})$$

where N is the total number of wires in the link,  $C_L$  and  $C_C$  are the self and coupling capacitance of a wire and neighboring wires respectively,  $\alpha_L$  is the switching activity on a wire and  $\alpha_C$  is the switching activity with respect to the adjacent wires,  $\tau$  is the short circuit period, V is the supply voltage, f is the clock frequency and  $I_{short}$ ,  $I_{bias, wire}$  and  $I_{leak,gate}$  are currents as explained before. Again, to summarize, the first two components are the dynamic components and the last component is the static component. To be more precise, the first component is due to switching activity within a wire and between wires, the second component is a result of short-circuit of the gate during switching.

# Chapter 4 **Design and Power Model of Register-based FIFOs**

# 4.1. Introduction

FIFO, acronym for "First in First out", is a concept used to describe the behaviour of a buffer. As the name says, it works according to the first-come first-serve principle.

A FIFO fundamentally consists of some storage elements from which data can be read or written to. The storage element may either be an SRAM [33][27] (static random access memory) or a DRAM [26] (dynamic random access memory) or a set of registers (flip-flops) or any other form of storage.

SRAM's are static in nature and provide data as long as power is provided. SRAM's are mainly used for their speed.

DRAM's are employed as separate individual memories due to their small size and lower cost than SRAM's. But they can be power hungry on account of their need for periodic refreshing.

Alternatively, registers are better than SRAMs and DRAMs for realising small memories due to their small size, cost effectiveness and simplistic organization. Current trend in NoC-based SoC's [28] is the usage of register-based buffers as they consume less energy than DRAM or SRAM solutions.

In general, irrespective of the type of memory used, buffering basically helps in managing the data traffic during congestion of packets (increased traffic) through the links in a network and during contention of resources (a situation where two or more sources compete for the same resource at the same time) in a large network.

In this chapter, we therefore analyse and focus on the power consumption of a router based FIFO buffer using registers. The energy consumed also depends on various factors and shall be discussed in this chapter and later on, a power model is given. In order to observe and analyse the effect of various parameters on energy consumption of a FIFO, several experiments are performed on FIFO buffers of various sizes.

# 4.2. Implementation of Register based FIFO Buffers

As explained earlier, FIFOs can either be SRAMs, DRAMs or registers. We focus on the latter solution which is the standard for NoCs. When focussing to the internals of a FIFO, the data (group of flits or words) is either multiplexed-demultiplexed (as in the current implementation described in section 4.2.1) or shifted using shift registers (refer to section 4.2.3) to the output of the FIFO [29][30][31]. We discuss these two alternatives briefly in subsequent subsections along with their pros and cons.

# 4.2.1 Implementation of 4-place FIFO Buffers

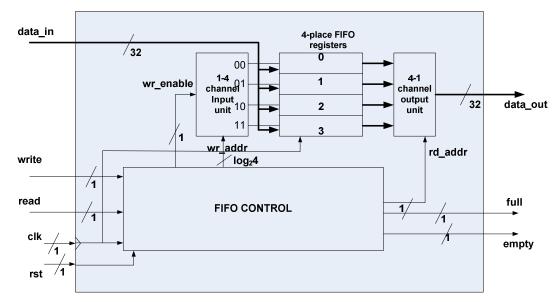

Figure 9 depicts the internal block diagram of a 4-place FIFO buffer. It is mainly composed of a FIFO control unit, a 1-to-4 channel input unit (similar to a de-multiplexer), a 4-to-1 channel output unit (similar to a multiplexer) and four registers to store the data.

Figure 9: 4-place FIFO buffer

The interfaces to the FIFO at the input side are the read, write and input data signals apart from the clock and the reset signal, while at the output, the interfaces are the output data, full and empty signals. Internally there are signals such as the write and read address pointers and a write enable signal which are controlled by the FIFO control unit. In addition, the reset signal is used to initialize the write and read address pointers to a steady state, which is the empty state of the FIFO, to avoid abnormal behaviour of the FIFO. Further, the usage of the clock is such that changes occur only at the rising or falling clock edge depending on the requirements.

As explained earlier, the FIFO control unit controls the functioning of the whole FIFO. It controls and updates the read and write address pointers. It also informs the outside world about the full and empty status of the FIFO. The 1-to-4 channel input unit lets the data to be written onto the correct FIFO place based on the write address generated from the FIFO control unit only when both the write action and write enable are true. Similarly, the 4-to-1 channel output unit lets the data to be read from the correct location based on the read address generated from the FIFO control unit.

The data arrives at the FIFO and with the write action issued, the data is written into the appropriate register place. The right location of the FIFO place is notified with the write enable signal together with the write signal going high. This is to ensure that the write action takes place only when at least one of the FIFO places is free, so that the data is not overwritten before a read action has taken place. Similarly, when the read action is issued, the data is read from the correct location, which in turn is controlled by the FIFO control unit. It ensures that the FIFO has at least one entry. When the FIFO is empty, on a read action, the previous data read will be revealed again.

# 4.2.2 Working of a 4-place FIFO buffer in terms of a behavioural FSM

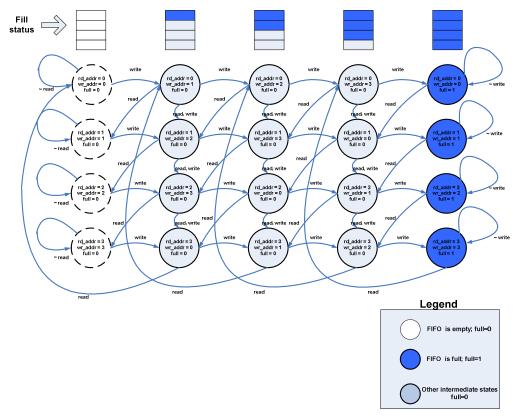

Figure 10: FSM of a 4-place FIFO buffer

The FIFO acts as a counter modulo the FIFO size. The states depicted here are ranked according to their fill status from left to right ranging from empty, one entry, and so on until the FIFO is full. Each of these states has four occurrences, depending on the precise value of the read and write pointers. If the FIFO is either empty or full, the read and write pointers point to the same location in the FIFO. Hence we define a variable full that is zero when empty and one when full. The five main FIFO states are represented as, 0(full=0), 1(full=0), 2(full=0), 3(full=0) and 0(full=1). Note that we differentiate the first and the last state with the status of the variable full. Further from Figure 10, we see that write and read actions can be performed simultaneously, provided the FIFO is neither full nor empty.

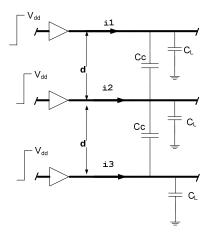

# 4.2.3 Alternate model of a FIFO buffer using shift registers

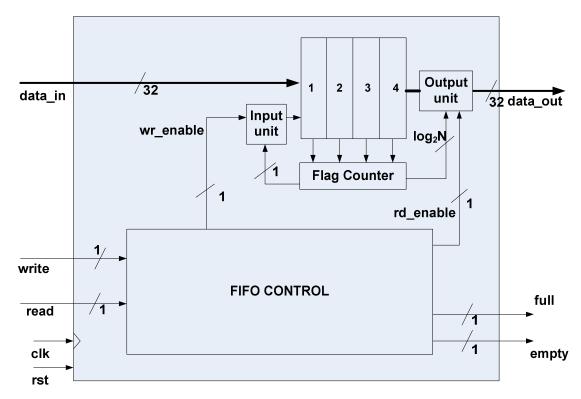

FIFO buffers can also be implemented using shift registers, refer Figure 11 [30]. Shift registers are primarily used to transfer data linearly from input to output. Fundamentally, shift registers are a set of registers arranged in a linear order with inputs connected to outputs in such a way that the data is shifted along its line when activated.

Figure 11: FIFO model with shift registers

Initially when a write action is issued, with the arrival of the data at the input, the previously available data in the FIFO is shifted one position towards the output depending upon the availability of space in the buffer. On a read action, data is forwarded towards the output of the FIFO from the first location containing valid data. The information regarding space availability and location of data is given by the flag counter.

### 4.2.4 Pros and Cons of the above two architectures

A FIFO buffer as implemented in section 4.2.1 is a better option over a FIFO architecture as implemented in section 4.2.3 as there is no delay in extracting the data from the FIFO buffer. In the latter case, the data has to shift as many places as FIFO buffers and this introduces latency. A drawback of the former architecture is that it requires multiplexers and de-multiplexers sized according to the number of FIFO places. This adds to area and power consumed.

Shift registers are useful if a small number of shift stages is used (<8), otherwise, it may lead to overloading of the data path if too many stages are connected. Even in case of a low number of shift stages, for e.g., 4 stages, we see that there is a latency of 4 clock cycles for data to traverse through the shift registers, assuming that the time taken by the data to shift between successive places is one clock cycle. Thus it is almost never recommended when compared to the FIFO buffers as shown in Figure 10.

# 4.3. Power model for a FIFO

Power consumption in a FIFO is due to reading and writing the data, clock activity, internal short circuit and leakage. The first four components form the dynamic part of the power consumption. This dynamic component can be further divided into power consumption due to switching activity and due to internal short-circuits that occur during switching. Hence the total power consumption is modelled as follows.

$$P_{total} = P_{write} + P_{read} + P_{clk} + P_{int} + P_{leak}$$

The first three components  $P_{read}$ ,  $P_{write}$  and  $P_{clk}$  form the switching power of the dynamic component. Further  $P_{read}$  and  $P_{write}$  are influenced by the power consumed by the control part and due to the data part, the switching activity. The control part includes the power consumed by the control bits, i.e., the write and read signals and the FIFO control unit. The data part includes the power consumed due to registers and the flipping of bits.

In a write operation, the power consumed per time unit is the result of the power consumed by the FIFO control unit combined with the 1-to-n channel input unit in decoding the write address, along with the power consumed to store the incoming data in the FIFO.

$$P_{write} = r_w.P_{ctrl} + \alpha_F.P_{store}$$

Here,  $r_w$  is the rate at which write actions occur and  $\alpha_F$  is the amount of 0 to 1 and 1 to 0 bit flips occurring between the incoming data and 'F' is a subscript for FIFO.  $P_{ctrl}$  and  $P_{store}$  are the average power consumed at the control unit for one write action and the power consumed to store the data in the FIFO respectively. Note that  $\alpha_F.r_w$  in this context is the same parameter as  $\alpha_L$  in the previous chapter.

Similarly in a read operation, the power consumed per time unit is the result of the power consumed by the FIFO control unit combined with the 4-to-1 channel output unit in encoding the read address along with the power consumed to retrieve the data from the FIFO.

$$P_{read} = r_r P_{ctrl} + \alpha_F P_{retreive}$$

Here,  $r_r$  is the rate at which read actions occur and  $\alpha_F$  is the amount of 0 to 1 and 1 to 0 bit flips occurring between the outgoing data. In the long run,  $r_r = r_w = r$ .  $P_{ctrl}$  and  $P_{retrieve}$  is the power consumed at the control unit and the power consumed to retrieve the data from the FIFO respectively. It is assumed that the average power consumed for the control of one read action equals the power consumed for controlling one write action.

Apart from the power consumed by write and read activities, there is another component namely the  $P_{clk}$ . Clock activity causes permanent constant power consumption due to switching activity.

The other component of the dynamic power is the internal power  $P_{int}$  which is the result of the internal short circuits occurring during switching of bits in the incoming data, the switching of read and write actions and clock activity. Therefore  $P_{int}$  can be calculated as follows,

$$P_{int} = k1.r + k2.\alpha_F + k3$$

Here, r is the rate of read and write actions and  $\alpha_F$  is the amount of bit flips. The constants k1 and k2 are respectively the average internal power consumed for the control of read and write actions and due to bit changes in data and k3 is due to the clock activity. This varies

with varying clock frequencies. The static power component, i.e., the leakage power  $P_{leak}$ , is assumed to be a constant.

Substituting the detailed power models for the individual components in Ptotal, we get

$$P_{total} = (2P_{ctrl} + k_1)r + \alpha_F(P_{store} + P_{retrieve} + k_2) + k_3 + P_{clk} + P_{leak}$$

# 4.4. Experiments and Results

### 4.4.1. Functional Verification of the model

In order to verify the FIFO model, several experiments are performed with different input vectors, different write and read patterns and different cases, some of which are mentioned below. On the whole the complete functional behavior is verified.

- 1. Full and empty status of the buffers.

- 2. Switching activity of the data bits (only zeros, only ones, different combinations of zeros and ones).

- 3. Alternate read and write actions.

- 4. Bursts of read and write actions.

A testbench is written to validate the functionality of the design with different situations and different test vectors. Both the design and the testbench are implemented in Verilog.