| MASTER                                                                         |

|--------------------------------------------------------------------------------|

| Power models of system-on-chip and external memory for multimedia applications |

|                                                                                |

| Chinta, A.                                                                     |

| Award date: 2006                                                               |

|                                                                                |

| Link to publication                                                            |

This document contains a student thesis (bachelor's or master's), as authored by a student at Eindhoven University of Technology. Student theses are made available in the TU/e repository upon obtaining the required degree. The grade received is not published on the document as presented in the repository. The required complexity or quality of research of student theses may vary by program, and the required minimum study period may vary in duration.

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 17. Jun. 2025

# **TECHNISCHE UNIVERSITEIT EINDHOVEN Department of Mathematics and Computer Science**

# POWER MODELS OF SYSTEM-ON-CHIP AND EXTERNAL MEMORY FOR MULTIMEDIA APPLICATIONS

By Anuradha Chinta

Supervisors: Dr. Ir. Marc Geilen Ms. DRS. EFM Steffens

#### **ACKNOWLEDGEMENTS**

I would like to gratefully acknowledge the enthusiastic supervision of Dr. Ir. Marc Geilen, Assistant Professor at the Electrical Engineering department of Technical University Eindhoven and Ms. DRS.EFM Steffens, Senior Research Scientist at Philips Research Labs, Eindhoven for their invaluable technical guidance and support provided during this thesis work. I would like to thank them for providing me with an opportunity to carry out my M.Sc project at Philips Research Labs, Eindhoven.

I would like to thank Ms. LIC.CM Otero Perez at Philips Research Labs, Eindhoven for helping me with the tools and clarifying my doubts patiently. I would like to thank Mr. Ir. AT Burchard at Philips Research Labs, Eindhoven for his invaluable time and help with measurements, analysis and numerous stimulating discussions.

I am also thankful to Alina, PhD student for clearing my doubts. I wish to thank my classmates in TU/e for their help and support during my study program.

I thank my husband Subrahmanya Kumar and our families for their constant encouragement and moral support throughout my study period.

#### A. ABSTRACT

The multimedia functionality in modern handheld devices is computationally intensive and requires a lot of energy. The source of energy in these devices is usually a battery. Battery technology has not improved at the pace of increase in energy requirements. An important requirement in these devices is to reduce power consumption while meeting the timing constraints of multimedia applications. Multimedia applications have the advantage of allowing run time trade-offs between (picture) quality and power consumption. The (picture) quality and hence the power consumption can be controlled by application parameters. In order to allow for run time trade-offs, one needs to have an estimate of power consumption for various application parameter settings.

This thesis focuses on developing power models for a System-on-Chip and Double Data Rate (DDR) memory from application parameters. The power models were developed through physical measurements on a Philips PNX1500 platform by running MPEG-4 decoder application. We present two methods to develop power models. The first method develops power models at a higher abstraction level by excluding architecture level details, whereas the second method considers architecture level details. Power models developed with the first method are abstract and easy to model, but the validity of the models is limited to this specific platform. The architecture level details of the second method can be projected to other platforms. In this thesis, we also show that the architecture level details can be used to derive the scalable frequencies for dynamic frequency scaling method. The experiments with two input streams of different content suggest that the content of the input stream has no influence on power models.

## **B. TABLE OF CONTENTS**

| A( | CKNOWLEDGEMENTS                                                 | Il       |

|----|-----------------------------------------------------------------|----------|

| A. | ABSTRACT                                                        | III      |

| В. | TABLE OF CONTENTS                                               | IV       |

|    | ABBREVIATIONS                                                   |          |

|    | LIST OF FIGURES                                                 |          |

|    |                                                                 |          |

|    | LIST OF TABLES                                                  |          |

| F. | LIST OF GRAPHS                                                  | X        |

| 1  | INTRODUCTION                                                    | 1        |

|    | 1.1 PROBLEM DESCRIPTION                                         | 1        |

|    | 1.2 ENERGY VS. POWER CONSUMPTION                                |          |

|    | 1.3 APPROACH                                                    |          |

|    | 1.3.1 Black box approach                                        |          |

|    | 1.3.2 White box approach                                        |          |

| _  |                                                                 |          |

| 2  | PHILIPS PNX1500 AND TOOLS                                       |          |

|    | 2.1 PNX1500                                                     |          |

|    | 2.2 Tools                                                       |          |

|    | 2.2.1 dvpMon                                                    |          |

|    | 2.2.2 URD (Universal Register Debugger)                         |          |

|    |                                                                 |          |

| 3  | EXPERIMENTAL SETUP AND MEASUREMENTS                             | 10       |

|    | 3.1 Introduction                                                |          |

|    | 3.2 EXPERIMENTAL SETUP                                          |          |

|    | 3.3 POWER MEASUREMENTS                                          |          |

|    | 3.4 Errors                                                      |          |

| 4  | ENERGY AND POWER MODELS FOR THE CPU AND MEMORY                  | 13       |

|    | 4.1 Introduction                                                | 13       |

|    | 4.2 POWER CONSUMPTION OF A CMOS CIRCUIT                         |          |

|    | 4.3 ENERGY CONSUMPTION OF AN EMBEDDED PROCESSOR AND MEMORY      |          |

|    | 4.4 ENERGY AND POWER CONSUMPTION MODELS FOR CPU AND MEMORY      |          |

|    | 4.4.1 Energy and Power consumption models for CPU               |          |

|    | 4.4.2 Energy and Power consumption models for Memory            |          |

| _  | •                                                               |          |

| 5  | POWER MODELS FOR SYSTEM-ON-CHIP (SOC)                           | 20       |

|    | 5.1 Introduction                                                |          |

|    | 5.2 WHITE BOX APPROACH EXPERIMENTS AND RESULTS                  |          |

|    | 5.2.1 Power consumption in idle state                           |          |

|    | 5.2.2 Power consumption in stall state                          |          |

|    | 5.2.4 Linear regression                                         |          |

|    | 5.3 EXPERIMENTS WHEN CPU IS IN POWER DOWN MODE                  |          |

|    | 5.3.1 Power consumption in idle and stall states                |          |

|    | 5.3.2 Linear equation solutions                                 |          |

|    | 5.3.3 Linear regression                                         |          |

|    | 5.4 REFINED POWER CONSUMPTION MODEL                             |          |

|    | 5.4.1 Experiments                                               |          |

|    | 5.4.2 Further simplification of the SoC power consumption model |          |

|    | PARAMETERS                                                      |          |

|    | 5.5.1 Models relating t to the FR & FS                          | 35<br>35 |

|                                                    | 5.5.2                                                                                     | Model relating t <sub>cpu,stall</sub> to the FR and FS                                                                                         | 38                                                 |

|----------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

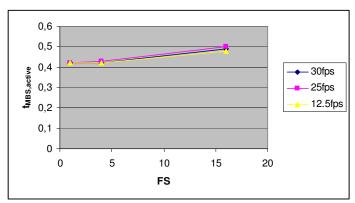

|                                                    | 5.5.3                                                                                     | Model relating t <sub>MBS,active</sub> to the FS                                                                                               | 39                                                 |

| 5                                                  | .6                                                                                        | COMPOSITIONAL MODEL FOR THE WHITE BOX APPROACH                                                                                                 |                                                    |

| 5                                                  | .7                                                                                        | BLACK BOX APPROACH TO RELATE THE AVERAGE POWER CONSUMPTION OF SOC TO FR A                                                                      | ND                                                 |

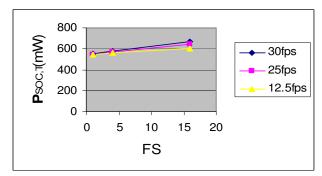

| F                                                  | S                                                                                         | 41                                                                                                                                             |                                                    |

| 5                                                  | .8                                                                                        | COMPARISON OF THE WHITE BOX AND BLACK BOX MODELS                                                                                               | 42                                                 |

|                                                    | POW                                                                                       | ER MODELS FOR MEMORY                                                                                                                           | 44                                                 |

| 6                                                  | .1                                                                                        | INTRODUCTION                                                                                                                                   | 44                                                 |

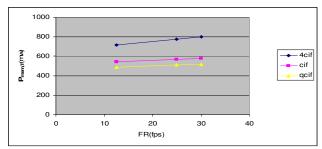

|                                                    | 5.2                                                                                       | BLACK BOX APPROACH EXPERIMENTS AND RESULTS                                                                                                     |                                                    |

|                                                    | 6.2.1                                                                                     | Without CPU power down                                                                                                                         |                                                    |

|                                                    | 6.2.2                                                                                     | With CPU power down                                                                                                                            |                                                    |

| 6                                                  | 5.3                                                                                       | WHITE BOX APPROACH EXPERIMENTS AND RESULTS                                                                                                     |                                                    |

|                                                    | 6.3.1                                                                                     | Measurement of application dependent platform parameters through experiments                                                                   |                                                    |

|                                                    | 6.3.2                                                                                     | Calculation of application independent platform parameters through linear regression 50                                                        |                                                    |

|                                                    | 6.3.3                                                                                     | Simplified model                                                                                                                               | 51                                                 |

| 6                                                  | .4                                                                                        | MODELS RELATING APPLICATION DEPENDENT PLATFORM PARAMETERS TO APPLICATION                                                                       |                                                    |

| P                                                  | ARAME                                                                                     | TERS                                                                                                                                           | 52                                                 |

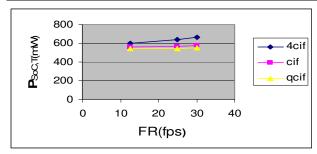

|                                                    | 6.4.1                                                                                     | Models relating t <sub>mem,active</sub> to the FR and FS                                                                                       | 52                                                 |

|                                                    | 6.4.2                                                                                     | Models relating t <sub>mem,read</sub> to the FR and FS                                                                                         |                                                    |

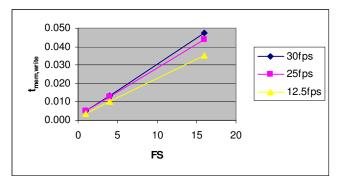

|                                                    | 6.4.3                                                                                     | Models relating t <sub>mem,write</sub> to the FR and FS                                                                                        |                                                    |

| 6                                                  | 5.5                                                                                       | COMPOSITIONAL MODEL FOR THE WHITE BOX APPROACH                                                                                                 |                                                    |

| 6                                                  | .6                                                                                        | COMPARISON OF THE WHITE BOX AND BLACK BOX MODELS (WITHOUT CPU POWER DOWN                                                                       | v)56                                               |

|                                                    |                                                                                           | GRATED POWER MODEL FROM THE POWER MODELS OF SOC AND  Introduction                                                                              | 58                                                 |

|                                                    | .2                                                                                        |                                                                                                                                                | 58                                                 |

| ·                                                  | 7.2.1                                                                                     |                                                                                                                                                |                                                    |

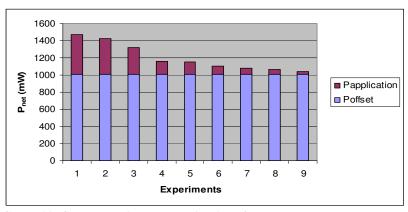

|                                                    |                                                                                           | INTEGRATED POWER MODEL                                                                                                                         | 58                                                 |

|                                                    |                                                                                           | Integrated power model                                                                                                                         | 58<br>58                                           |

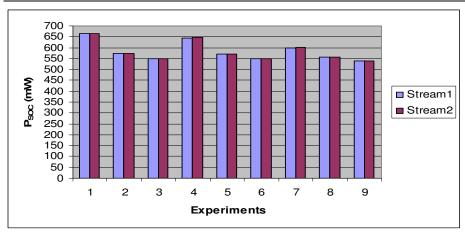

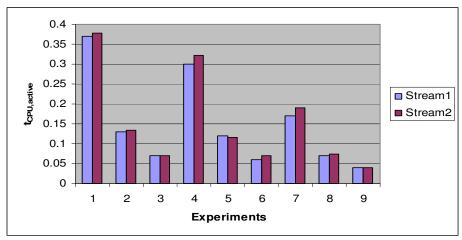

|                                                    | SOC                                                                                       | INTEGRATED POWER MODEL  Analysis  AND MEMORY EXPERIMENTS WITH A DIFFERENT INPUT STREAM                                                         | 58<br>58<br><b>61</b>                              |

| 8                                                  | <b>SOC</b>                                                                                | INTEGRATED POWER MODEL  Analysis  AND MEMORY EXPERIMENTS WITH A DIFFERENT INPUT STREAM  INTRODUCTION.                                          | 58<br>58<br><b> 61</b><br>61                       |

| 8                                                  | SOC<br>.1<br>.2                                                                           | INTEGRATED POWER MODEL  Analysis  AND MEMORY EXPERIMENTS WITH A DIFFERENT INPUT STREAM  INTRODUCTION  EXPERIMENTS AND RESULTS                  | 58<br>58<br><b> 61</b><br>61                       |

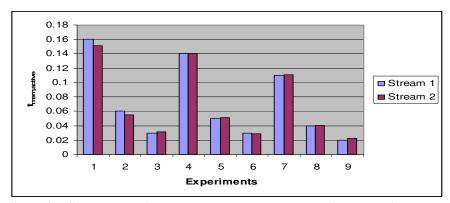

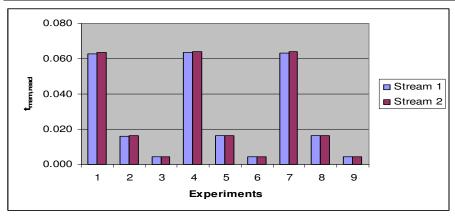

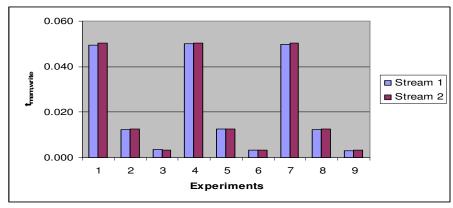

| 8                                                  | SOC<br>3.1<br>3.2<br>8.2.1                                                                | INTEGRATED POWER MODEL  Analysis  AND MEMORY EXPERIMENTS WITH A DIFFERENT INPUT STREAM  INTRODUCTION  EXPERIMENTS AND RESULTS  SoC experiments | 58<br>58<br><b>61</b><br>61                        |

| 8                                                  | SOC<br>.1<br>.2<br>8.2.1<br>8.2.2                                                         | INTEGRATED POWER MODEL  Analysis                                                                                                               | 58<br>58<br>61<br>61<br>64                         |

| 8                                                  | SOC<br>3.1<br>3.2<br>8.2.1<br>8.2.2                                                       | INTEGRATED POWER MODEL  Analysis                                                                                                               | 58<br>58<br>61<br>61<br>64<br>65                   |

| 8                                                  | SOC<br>3.1<br>3.2<br>8.2.1<br>8.2.2                                                       | INTEGRATED POWER MODEL  Analysis                                                                                                               | 58<br>58<br>61<br>61<br>64<br>65                   |

| 8 8                                                | SOC<br>3.1<br>3.2<br>8.2.1<br>8.2.2                                                       | INTEGRATED POWER MODEL  Analysis                                                                                                               | 58<br>58<br>61<br>61<br>64<br>65<br>65             |

| 8 8 8                                              | SOC<br>3.1<br>3.2<br>8.2.1<br>8.2.2<br>3.3<br>EFFI                                        | INTEGRATED POWER MODEL  Analysis                                                                                                               | 58<br>58<br>61<br>61<br>64<br>65<br>65             |

| 88 88 88 99 99                                     | SOC<br>.1<br>.2<br>.8.2.1<br>.8.2.2<br>.3<br>EFFI                                         | INTEGRATED POWER MODEL  Analysis                                                                                                               | 588<br>611<br>611<br>612<br>652<br>653<br>653      |

| 8                                                  | SOC<br>3.1<br>3.2<br>8.2.1<br>8.2.2<br>3.3<br>EFFI<br>3.1<br>3.2                          | INTEGRATED POWER MODEL  Analysis                                                                                                               | 58<br>58<br>61<br>61<br>61<br>64<br>65<br>67<br>67 |

| 88<br>88<br>9<br>9<br>9                            | SOC<br>3.1<br>3.2<br>8.2.1<br>8.2.2<br>3.3<br>EFFI<br>3.1<br>3.2<br>3.3                   | INTEGRATED POWER MODEL  Analysis                                                                                                               | 58<br>58<br>61<br>61<br>65<br>65<br>67<br>69       |

| 88<br>88<br>99<br>99                               | SOC<br>3.1<br>3.2<br>8.2.1<br>8.2.2<br>3.3<br>EFFI<br>3.1<br>3.2<br>3.3<br>CON            | INTEGRATED POWER MODEL  Analysis                                                                                                               | 58616161636565676970                               |

| 8<br>8<br>8<br>9<br>9<br>9<br>0<br>REI             | SOC<br>3.1<br>3.2<br>8.2.1<br>8.2.2<br>3.3<br>EFFI<br>3.1<br>2.2<br>3.3<br>CON<br>FERENDI | INTEGRATED POWER MODEL  Analysis                                                                                                               | 58616161636565676970                               |

| 88<br>89<br>99<br>90<br>80<br>80<br>80<br>80<br>80 | SOC 3.1 3.2 8.2.1 8.2.2 3.3 EFFI 3.2 3.3 CON FERENDI BUB BU                               | INTEGRATED POWER MODEL  Analysis                                                                                                               | 5861616163646567676772                             |

| 8<br>8<br>8<br>9<br>9<br>9<br>0<br><b>0</b>        | SOC 3.1 3.2 8.2.1 8.2.2 3.3 EFFI 3.2 3.3 CON FERENDI BUS M                                | INTEGRATED POWER MODEL  Analysis                                                                                                               | 58616162656567697273                               |

#### C. ABBREVIATIONS

4CIF 4 times Common Intermediate Format

A/D Analogue to Digital

API Application Programmers Interface

ASCII American Standard Code for Information Interchange

BETSY Being on Time Saves energY

BIS Boot Info Structure

CMOS Complementary Metal Oxide Semiconductor

CPU Central Processing Unit

CIF Common Intermediate Format

DCS Device Control and Status network

DDR SDRAM Double Data Rate Synchronous Dynamic Random Access Memory

DMA Direct Memory Access

DVP Digital Video Platform

EJTAG Enhanced JTAG

HD High Definition

IEEE Institute of Electrical and Electronics Engineers

ISR Interrupt Service Routine

JTAG Joint Test Action Group

LCD Liquid Crystal Display

MBS Memory Based Scalar

MMI Main Memory Interface

MMIO Memory Mapped Input Output

MPEG Moving Picture Experts Group

MPTK Media Processing Tool Kit

NDK Nxperia Developers Kit

OSAL Operating System Abstraction Layer

PC Personal Computer

PCI Peripheral Component Interconnect PMAN Pipelined Memory Access Network

PNX Philips NXperia

PSOS Portable Scalable Operating System

QVCP Quality Video Composition Processor

QCIF Quarter Common Intermediate Format

RMSE Root Mean Square Error RS232 Recommended Standard232

SoC System-on-Chip

TM TriMedia

URD Universal Register Debugger

VGA Video Graphics Array

## D. LIST OF FIGURES

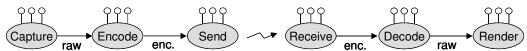

| Figure 1: End to End streaming                                                 | 2    |

|--------------------------------------------------------------------------------|------|

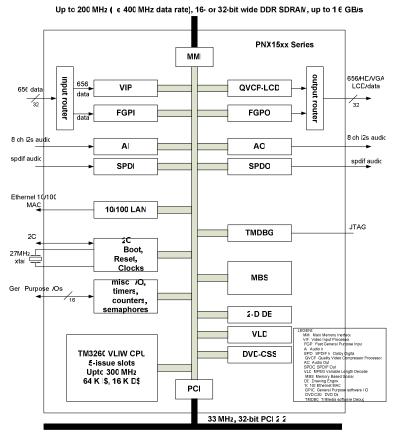

| Figure 2: Functional block diagram of PNX1500 SoC                              | 6    |

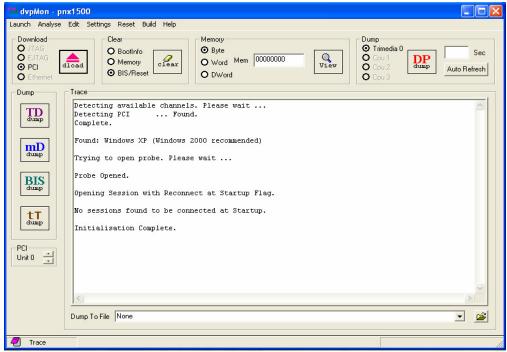

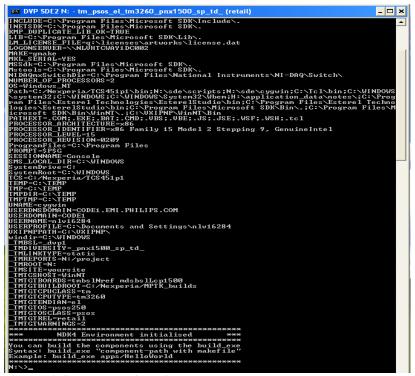

| Figure 3: Screenshot of dvpMon                                                 | 7    |

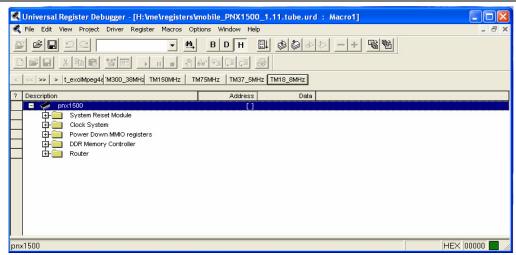

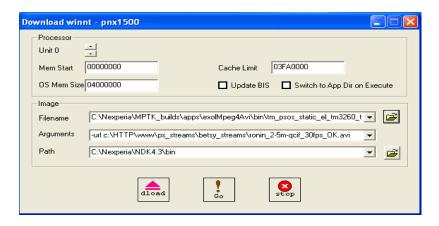

| Figure 4: Screen shot of URD                                                   | 8    |

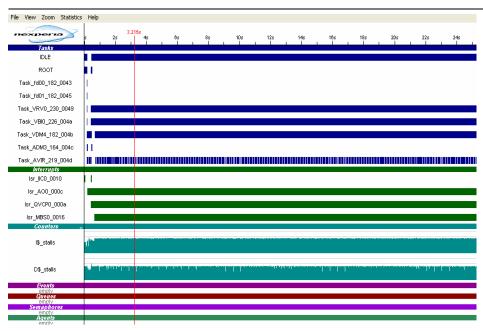

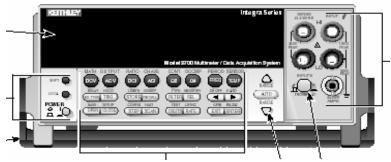

| Figure 5: Screenshot of Time Doctor Viewer                                     | 9    |

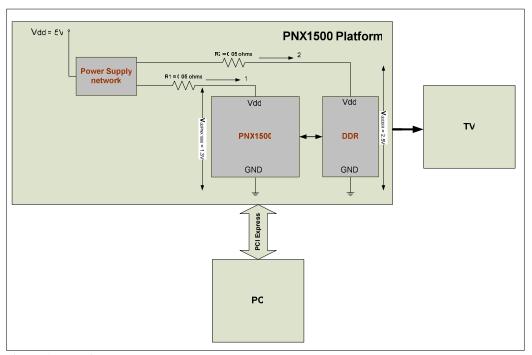

| Figure 6: Experimental set-up                                                  | . 10 |

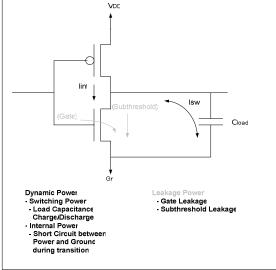

| Figure 7: Power dissipation in CMOS designs                                    | . 13 |

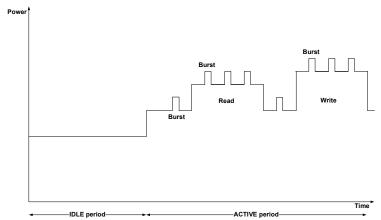

| Figure 8: Representation of memory power model given in Equation (10)          | . 18 |

| Figure 9: Representation of modified memory power model given in Equation (11) | 19   |

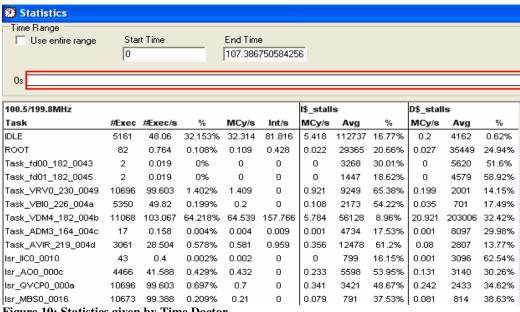

| Figure 10: Statistics given by Time Doctor                                     | . 21 |

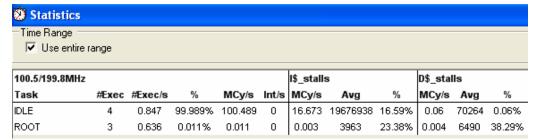

| Figure 11: Statistics given by TimeDoctor for idle_test program                | . 23 |

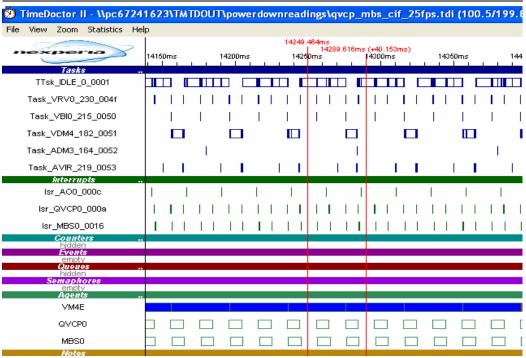

| Figure 12: Screen shot of TimeDoctor viewer                                    | . 31 |

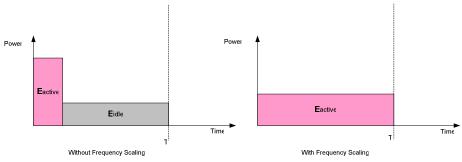

| Figure 13: Energy consumption without and with frequency scaling               | . 67 |

| Figure 14: Screen shot of ndk4_env.bat                                         | . 73 |

| Figure 15: Screen shot of dload.exe                                            | . 74 |

| Figure 16: Front panel of the multimeter                                       | . 74 |

## **E. LIST OF TABLES**

| Table 1: P <sub>SoC,T</sub> , t <sub>CPU,active</sub> , t <sub>CPU,stall</sub> and t <sub>CPU,idle</sub> values obtained through various                                         |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| experiments                                                                                                                                                                      | . 22 |

| Table 2: The calculated values for P <sub>CPU,active</sub> , P <sub>CPU,stall</sub> and P <sub>CPU,idle</sub>                                                                    | . 24 |

| Table 3: P <sub>SoC,T</sub> , t <sub>CPU,active</sub> , t <sub>CPU,stall</sub> and t <sub>CPU,idle</sub> values obtained through various                                         |      |

| experiments in CPU power down mode                                                                                                                                               | . 27 |

| Table 4: The values calculated for P <sub>CPU,active</sub> , P <sub>CPU,stall</sub> in CPU power down mode                                                                       | 28   |

| Table 5: Actual and model predicted values for the P <sub>SoC,T</sub>                                                                                                            |      |

| Table 6: P <sub>SoC,T</sub> , t <sub>CPU, active</sub> , t <sub>CPU, stall</sub> , t <sub>CPU, idle</sub> , t <sub>QVCP, active</sub> , t <sub>MBS, active</sub> values obtained |      |

| through various experiments                                                                                                                                                      | . 32 |

| Table 7: Actual and model predicted values for P <sub>SoC,T</sub>                                                                                                                |      |

| Table 8: Actual and model predicted values for P <sub>SoC,T</sub>                                                                                                                |      |

| Table 9: Actual and Model 1 predicted values for t <sub>CPU,active</sub>                                                                                                         |      |

| Table 10: Actual and Model 2 predicted values for t <sub>CPU,active</sub>                                                                                                        |      |

| Table 11: Summary of the models and their RMSEs                                                                                                                                  |      |

| Table 12: Summary of the models and their RMSEs                                                                                                                                  |      |

| Table 13: Actual and compositional model predicted values for P <sub>SoC,T</sub>                                                                                                 |      |

| Table 14: P <sub>SoC.T</sub> measured from different experiments                                                                                                                 |      |

| Table 15: Summary of the models and their RMSEs                                                                                                                                  |      |

| Table 16: P <sub>mem,T</sub> values measured for different combinations of FR and FS                                                                                             |      |

| Table 17: Summary of the models and their RMSEs                                                                                                                                  |      |

| Table 18: P <sub>mem,T</sub> values measured for different combinations of FR and FS                                                                                             |      |

| Table 19: Summary of the models and their RMSEs                                                                                                                                  | 47   |

| Table 20: Read and write cycles from CPU and DMA devices measured through                                                                                                        |      |

| TimeDoctor tool in different experiments without CPU power down mode                                                                                                             | 48   |

| Table 21: Read and write cycles from CPU and DMA devices measured through                                                                                                        |      |

| TimeDoctor tool in different experiments with CPU power down mode                                                                                                                | 49   |

| Table 22: CPU read/write cycles from/to the memory during idle and decoding task                                                                                                 | S    |

|                                                                                                                                                                                  | 49   |

| Table 23: Cache read/write misses and CPU read/write cycles from/to the memory                                                                                                   |      |

| during idle task                                                                                                                                                                 | 50   |

| Table 24: t <sub>mem,idle</sub> , t <sub>mem,active</sub> , t <sub>mem,read</sub> and t <sub>mem,write</sub> values calculated for different                                     |      |

| combinations of FR and FS                                                                                                                                                        | 51   |

| Table 25: Measured and model predicted values for P <sub>mem,T</sub> and the corresponding                                                                                       |      |

| RMSE                                                                                                                                                                             | 51   |

| Table 26: Summary of models and their RMSEs                                                                                                                                      |      |

| Table 27: Summary of models and their RMSEs                                                                                                                                      |      |

| Table 28: Summary of models and their RMSEs                                                                                                                                      | . 55 |

| Table 29: Measured and compositional model predicted values for $P_{mem,T}$ and the                                                                                              |      |

| corresponding RMSE                                                                                                                                                               | 56   |

| Table 30: Poffset and Papplication values calculated for different experiments                                                                                                   | . 59 |

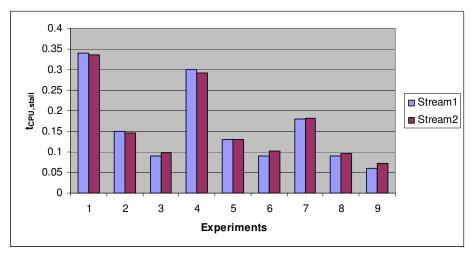

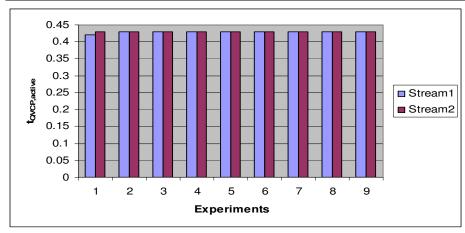

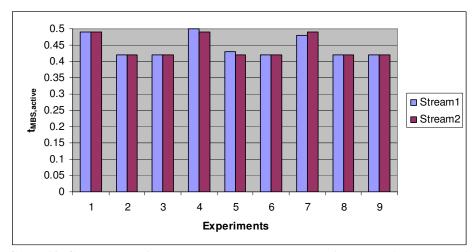

| Table 31: The P <sub>SoC,T</sub> , t <sub>CPU,active</sub> , t <sub>CPU,stall</sub> , t <sub>CPU,idle</sub> , t <sub>QVCP,active</sub> and t <sub>MBS,active</sub> values        |      |

| measured for Stream 2                                                                                                                                                            | 61   |

| Table 32: The maximum variation of the Stream 2 parameters with respect to the                                                                                                   |      |

| Stream 1 parameters                                                                                                                                                              | 63   |

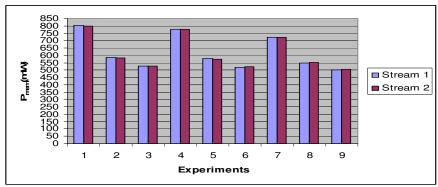

| Table 33: The P <sub>mem,T</sub> , t <sub>mem,idle</sub> , t <sub>mem,active</sub> , t <sub>mem,read</sub> and t <sub>mem,write</sub> values measured for                        |      |

| Stream2                                                                                                                                                                          | 64   |

| Table 34: The maximum variation of the Stream 2 parameters with respect to the                                                                                                   |      |

| Stream 1 parameters                                                                                                                                                              |      |

| Table 35: Scalable frequencies                                                                                                                                                   | . 68 |

| Table 36: SoC power consumption measured with frequency scalin | g for CPU power   |

|----------------------------------------------------------------|-------------------|

| down mode                                                      | 68                |

| Table 37: SoC power consumption measured with frequency scalin | g for without CPU |

| power down mode                                                | 69                |

## F. LIST OF GRAPHS

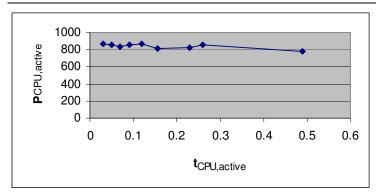

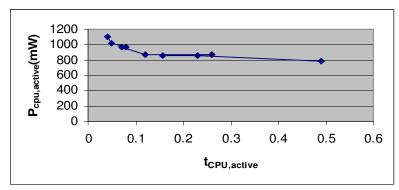

| Graph 1: Graph representing P <sub>CPU,active</sub> vs. t <sub>CPU,active</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 25 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

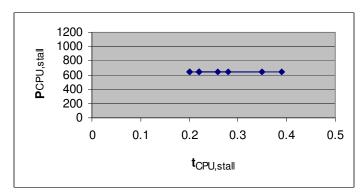

| Graph 2: Graph representing P <sub>CPU,stall</sub> vs. t <sub>CPU,stall</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

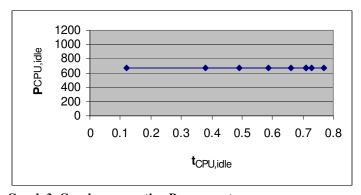

| Graph 3: Graph representing P <sub>CPU,idle</sub> vs. t <sub>CPU,idle</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |

| Graph 4: Graph representing P <sub>CPU,active</sub> vs. t <sub>CPU,active</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

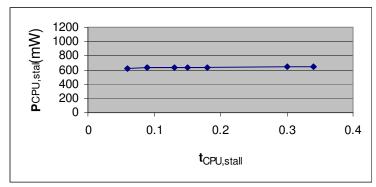

| Graph 5: Graph representing P <sub>CPU,stall</sub> vs. t <sub>CPU,stall</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

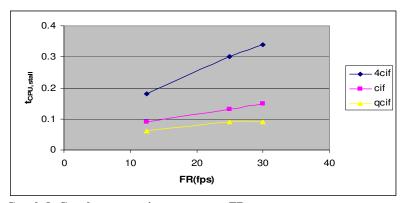

| Graph 6: Graph representing t <sub>cpu,active</sub> vs. FR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

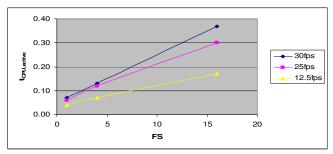

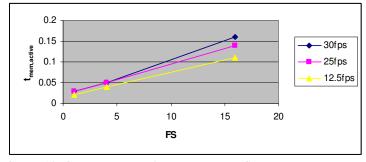

| Graph 7: Graph representing t <sub>cpu,active</sub> vs. FS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

| Graph 8: Graph representing t <sub>CPU,stall</sub> vs. FR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

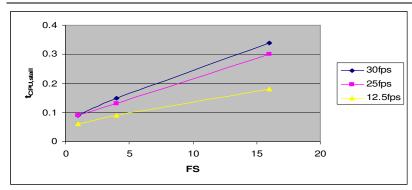

| Graph 9: Graph representing t <sub>CPU,stall</sub> vs. FS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| Graph 10: Graph representing t <sub>MBS, active</sub> vs. FS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| Graph 11: Graph representing P <sub>SoC,T</sub> vs. FR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| Graph 12: Graph representing P <sub>SoC,T</sub> vs. FS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42   |

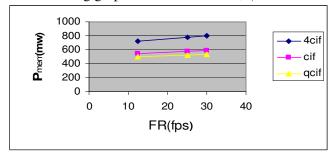

| Graph 13: Graph representing P <sub>mem,T</sub> vs. FR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 45   |

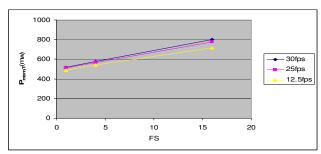

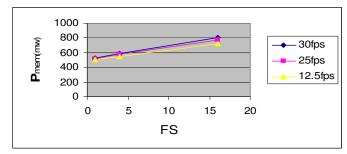

| Graph 14: Graph representing P <sub>mem,T</sub> vs. FS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| Graph 15: Graph representing P <sub>mem,T</sub> vs. FR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47   |

| Graph 16: Graph representing P <sub>mem,T</sub> vs. FS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47   |

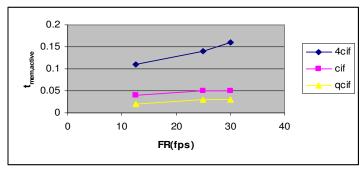

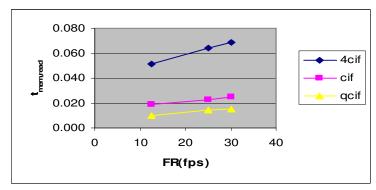

| Graph 17: Graph representing t <sub>mem,active</sub> vs. FR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 52 |

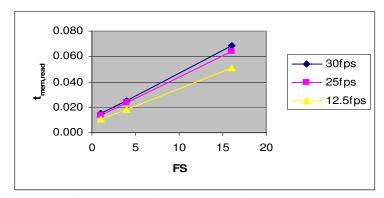

| Graph 18: Graph representing t <sub>mem,active</sub> vs. FS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 52 |

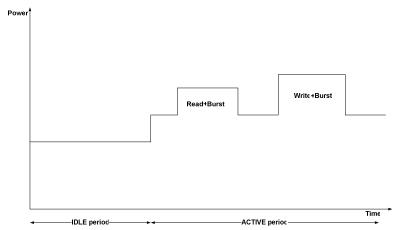

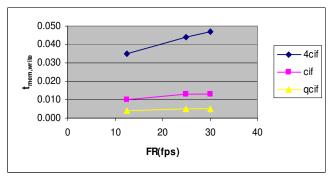

| Graph 19: Graph representing t <sub>mem,read</sub> vs. FR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 54 |